# Observation of Dynamic $V_{TH}$ of p-GaN Gate HEMTs by Fast Sweeping Characterization

Xiangdong Li<sup>®</sup>, *Member, IEEE*, Benoit Bakeroot, Zhicheng Wu<sup>®</sup>, Nooshin Amirifar, Shuzhen You<sup>®</sup>, Niels Posthuma<sup>®</sup>, Ming Zhao, Hu Liang, Guido Groeseneken<sup>®</sup>, *Fellow, IEEE*, and Stefaan Decoutere<sup>®</sup>

Abstract—In this work, fast sweeping characterization with an extremely short relaxation time was used to probe the  $V_{TH}$  instability of p-GaN gate HEMTs. As the  $I_D$ - $V_G$ sweeping time deceases from 5 ms to 5  $\mu$ s, the  $V_{\rm TH}$  dramatically degenerates from 3.13 V to 1.76 V, meanwhile the hysteresis deteriorates from 22.6 mV to 1.37 V. Positive bias temperature instability (PBTI) measurement by fast sweeping shows the  $V_{TH}$  features a very fast shifting process but a slower recovering process. D-mode HEMTs counterpart without Mg contamination demonstrates a negligible  $V_{TH}$ shift and hysteresis, proving the  $V_{TH}$  instability is probably due to the ionization of acceptor-like traps in the p-GaN depletion region. Finally, the  $V_{TH}$  instability is verified by a GaN circuit under switching stress. The  $V_{TH}$  instability under different sweeping speed uncovers the fact that the high  $V_{TH}$  by conventionally slow DC measurements is probably artificial. The DC V<sub>TH</sub> should be high enough to avoid HEMT faulty turn-on.

Index Terms— p-GaN gate HEMT, fast sweeping,  $V_{TH}$  shift, PBTI.

#### I. INTRODUCTION

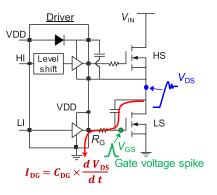

NHANCEMENT-MODE p-GaN gate HEMTs featuring a low gate charge  $Q_{\rm g}$ , a low on-resistance, and a fast switching capability have been penetrating the market of power electronics for years [1]–[3]. GaN power HEMTs are however vulnerable to faulty turn-on because of the fast switching characteristics. As shown by the bootstrap half-bridge circuitry in Fig. 1, after the low side (LS) switches OFF and the high side (HS) switches ON, the  $V_{\rm DS}$  of the LS switch will quickly soar to  $\sim V_{\rm IN}$  from 0 V within tens of nanoseconds. This swift voltage transient creates a miller current through the Miller capacitor  $C_{\rm DG}$  and the gate loop, inducing a gate voltage spike that in turn can falsely switch ON the LS switch [4].

Manuscript received January 18, 2020; revised February 1, 2020; accepted February 6, 2020. Date of publication February 10, 2020; date of current version March 24, 2020. This work was supported in part by the Vlaams Agenschap Innoveren en Ondernemen and the imec.icon research program. The review of this letter was arranged by Editor G. H. Jessen. (Corresponding author: Xiangdong Li.)

Xiangdong Li, Zhicheng Wu, and Guido Groeseneken are with the Department of Electrical Engineering, Katholieke Universiteit Leuven (KU Leuven), 3001 Leuven, Belgium, and also with imec, 3001 Leuven, Belgium (e-mail: xiangdong.li@imec.be).

Benoit Bakeroot is with the Center for Microsystems Technology (CMST), imec, 3001 Leuven, Belgium, and also with the Department of Electronics and Information Systems, Ghent University, 9052 Ghent, Belgium.

Nooshin Amirifar, Shuzhen You, Niels Posthuma, Ming Zhao, Hu Liang, and Stefaan Decoutere are with imec, 3001 Leuven, Belgium.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2020.2972971

Fig. 1. Schematic of a bootstrap half-bridge configuration, and the fast switching transient of HS device induces miller current that can result in faulty turn-on of the LS.

Suppressing the faulty turn-on necessitates a high threshold voltage  $V_{\text{TH}}$ , therefore some Schottky gate HEMTs have been adopted to boost the  $V_{\rm TH}$  to above 2.5 V. Nevertheless, the  $V_{\rm TH}$  instability of the Schottky gate has been widely reported [5]–[9]. Generally, the  $V_{\rm TH}$  instability is ascribed to several competing mechanisms occurring in the p-GaN/AlGaN stack, i.e., electron trapping, hole injection, and hole depletion. Tang et al. reported a  $V_{TH}$  positive shift at  $< 7 \text{ V } V_{GS}$  stress due to electron trapping at the p-GaN/AlGaN interface, and  $V_{\rm TH}$  decreases at > 7 V  $V_{\rm GS}$  stress because of the hole injection/electroluminescence (EL) [10]. Similar phenomena have also been observed with fast sweeping technique by Stockman *et al.* who claimed the electron trapping happens at the AlGaN/GaN interface whereas holes accumulate at the p-GaN/AlGaN interface or are trapped in the barrier layer [11]. He et al. [12] however demonstrated a monotonous positive V<sub>TH</sub> shift with fast-dynamic-stress method by a resistive-load setup [13]. Recently, more attention has been paid to use fast speed characterization to probe the  $V_{\rm TH}$  instability [5], [11].

In this work, the  $V_{\rm TH}$  instability will be investigated by a new fast sweeping characterization. The  $I_{\rm D}$ - $V_{\rm G}$  hysteresis,  $V_{\rm TH}$  shifting and recovery process, and the positive bias temperature instability (PBTI) will all be precisely probed, which provides some novel results undiscovered by conventional DC sweeping characterization.

# II. EPITAXY, FABRICATION, AND CIRCUIT

The pGaN/AlGaN/GaN structure was epitaxially grown using a metalorganic chemical vapor deposition (MOCVD) on 200 mm GaN-on-Si substrates. The epi stack consists of a 200 nm AlN nucleation layer, a 1.65  $\mu$ m (Al)GaN superlattice

0741-3106 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

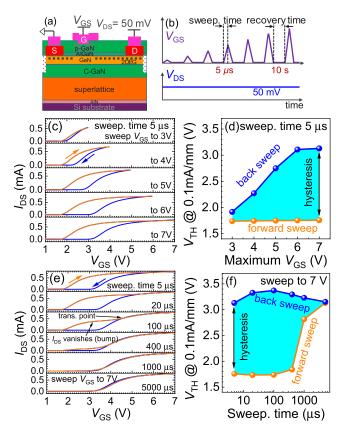

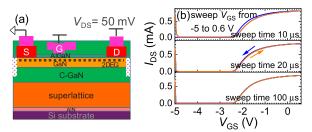

Fig. 2. (a) Cross-sectional schematic of the measured p-GaN gate HEMTs, (b) test waveforms, (c)  $I_{\rm D}$ - $V_{\rm G}$  curves and (d)  $V_{\rm TH}$  of the devices swept to various maximum  $V_{\rm GS}$ , and (e)  $I_{\rm D}$ - $V_{\rm G}$  curves and (f)  $V_{\rm TH}$  of the devices under various sweeping times of 5  $\mu$ s, 20  $\mu$ s, 100  $\mu$ s, 400  $\mu$ s, 1000  $\mu$ s, and 5000  $\mu$ s.

layer, a 1  $\mu$ m carbon-doped GaN back barrier, a 400 nm undoped GaN channel layer, a 12.5 nm Al<sub>0.235</sub>GaN barrier layer, and a 80 nm Mg-doped p-GaN layer with a dopant concentration of  $\sim 3\times 10^{19}$  cm<sup>-3</sup>. The processing details have been elaborated in [14]–[16]. The measured p-GaN gate HEMTs as shown in Fig. 2(a) have a gate width  $W_{\rm G}$  of 100  $\mu$ m, a gate length  $L_{\rm G}$  of 1.3  $\mu$ m, a gate-source distance  $L_{\rm GS}$  of 0.5  $\mu$ m, and a gate-drain distance  $L_{\rm GD}$  of 5.75  $\mu$ m. The fast sweeping characterization is performed using a Keysight B1530A WGFMU (Waveform Generator/ Fast Measurement Unit). Fig. 2(b) documents an example of the test waveform: the ultra-fast transient (down to  $\sim$ 2  $\mu$ s) is enabled by a 50  $\Omega$  output impedance in WGFMU which prevents reflection-induced waveform degradation. The function generator is an Agilent 81110A and the oscilloscope is a LeCroy HDO6054.

#### III. RESULTS AND DISCUSSION

The HEMTs were first subjected to double fast sweeping characterization. Fig. 2 (b) shows the  $V_{\rm DS}$  was fixed at 50 mV and the  $V_{\rm GS}$  swept from 0 V to a higher voltage and then back to 0 V. Between each double sweeping, 10 s relaxation time was inserted to ensure a full recovery of the  $V_{\rm TH}$  shift. Sweeping speeds are defined by the single sweeping time ranging from 5  $\mu$ s to 5000  $\mu$ s. Fig. 2 (c) and (d) show that a significant  $V_{\rm TH}$  hysteresis of up to 1.37 V is observed for

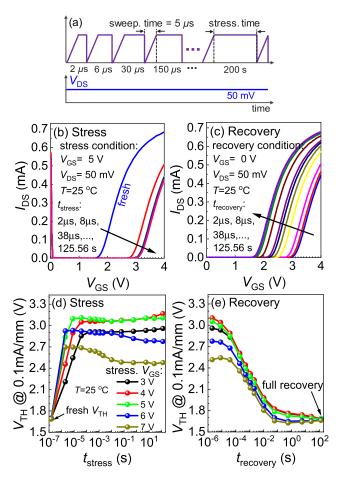

Fig. 3. (a) Sketches of PBTI measurement sequences by fast sweeping of 5  $\mu$ s in this work,  $I_{\rm D}$ - $V_{\rm G}$  curves during the (b) stress phase and (c) recovery phase by stress  $V_{\rm GS}$  of 5 V, and  $V_{\rm TH}$ -evolution under different stress  $V_{\rm GS}$  from 3 to 7 V during the (d) stress phase and (e) recovery phase at 25 °C. The sensing  $V_{\rm GS}$  sweeps from 0 to 4 V in 5  $\mu$ s.

the maximum  $V_{\rm GS}$  of 7 V, for the sweeping time of 5  $\mu$ s. By increasing the sweeping time, a transition point emerges on the forward sweep curve as shown in Fig. 2 (e), inducing a current bump observed previously [17]. The high current before this point gradually vanishes when sweeping time reaches 1000  $\mu$ s, thus inducing an arbitrarily high  $V_{\rm TH}$  as the conventional DC sweeping.

PBTI measurements were then conducted to investigate the  $V_{\text{TH}}$  behavior during the gate stress and recovery phases by the fast sweeping characterization. During the measurement, as demonstrated in Fig. 3(a), the stress was periodically interrupted to measure the  $I_D$ - $V_G$  characteristics by sweeping the  $V_{GS}$  from 0 to 4 V in 5  $\mu$ s (Fig. 3 (b)). The recovery behavior was monitored similarly except the  $V_{GS}$  was 0 V. The  $V_{\rm TH}$  relaxation is ubiquitous in BTI stressing [18]. Improper sampling precision might induce a fake conclusion [12]. In this work, the relaxation time between the stress and sense was limited to as short as 50 ns. Fig. 3 (d) shows that the  $V_{\rm TH}$ under lower stress  $V_{\rm GS}$  of 3 V takes  $\sim 200~\mu \rm s$  to saturate. In contrast, only  $\sim 2 \mu s$  has been enough for the stress  $V_{GS}$ of 6 V. Compared with the shifting process, the recovery process is much slower. Importantly, the  $V_{TH}$  shift is fully recoverable as shown in Fig. 3(e). It is worth to mention that

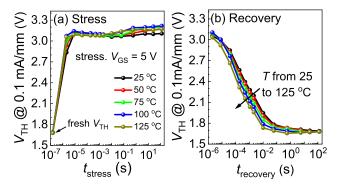

Fig. 4. Temperature-dependent  $V_{\rm TH}$  evolution under stress  $V_{\rm GS}$  of 5 V during the (a) stress and (b) recovery phases at the temperatures from 25 to 125 °C. The sensing  $V_{\rm GS}$  sweeps from 0 to 4 V in 5  $\mu$ s.

Fig. 5. (a) Cross-sectional schematic and (b) double-sweep  $I_{\rm D}\text{-}V_{\rm G}$  curves on the D-mode HEMTs on a D-mode epitaxy wafer without Mg contamination.

the  $V_{\text{TH}}$  will be very stable after the initial stress in application before shutdown, considering the operation  $V_{\text{GS}}$  in power ICs is around 5 V.

Temperature-dependent PBTI measurement results are demonstrated in Fig. 4. The impact of temperature on the  $V_{\rm TH}$  shift is not clearly discernable because of the very fast trapping process as shown in Fig. 4(a). Fig. 4 (b) shows that the recovery can be facilitated by high temperatures.

Locating the cause for the dynamic  $V_{\rm TH}$  is very challenging. Counterpart depletion-mode (D-mode) HEMTs on a D-mode epitaxy wafer were characterized, as shown in Fig. 5(a). The D-mode wafer has a similar superlattice buffer layer, but the epitaxy terminates after the AlGaN barrier and a thin GaN cap layer, without the p-GaN layer nor Mg out-diffusion in the AlGaN barrier and GaN channel [19]. Fig 5(b) shows a negligible hysteresis and  $V_{\rm TH}$  shift, proving that the  $V_{\rm TH}$  instability is a signature of the p-GaN, probably via the trapping by Mg or related impurities/complexes.

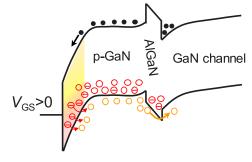

There have been plenty of reports about the enormous acceptor-like traps in the p-GaN layer above the top of the valence band [20]–[24], which are however ignored by the previous research on p-GaN gate HEMTs. Activated but unionized Mg, Mg-H complex, Mg-N-H complex, and other Mg-related traps are all possibly responsible for the  $V_{\rm TH}$  shift. As shown in Fig. 6, when the gate is positively biased and the depletion region extended, those acceptor-like traps in the p-GaN depletion region will be quickly ionized and release holes to the valence band. After the positive bias is removed, these ionized traps cannot be quickly deionized, inducing a positively shifted  $V_{\rm TH}$ . The  $V_{\rm TH}$  decrease for stress  $V_{\rm GS}$  of 6 and 7 V is possibly due to donor traps ionization or hole accumulation.

Fig. 6. Schematic band diagram of the metal/p-GaN/AlGaN/GaN gatestack under a positive gate bias. The acceptor-like traps in the depletion region (shaded region) will be ionized and induce net negative charges in the p-GaN layer, after removing the gate bias these traps cannot be quickly deionized.

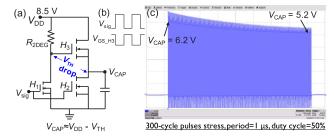

Fig. 7. (a) Schematic of the GaN IC to test the  $V_{\rm TH}$  evolution under 1 MHz switching stress, (b) waveforms of the  $V_{\rm sig}$  and  $V_{\rm GS\_H3}$ , and (c) switching waveform of  $V_{\rm CAP}$  during the 1 MHz, 300  $\mu \rm s$  stress shows the  $V_{\rm CAP}$  decrease from 6.2 to 5.2 V.

A GaN IC as sketched in Fig. 7(a) was submitted to a 1 MHz and 50% duty cycle switching stress test to verify the appearance of a dynamic  $V_{\rm TH}$  in a realistic application. This GaN IC is an integrated push-pull gate driver [25]. The IC was powered by  $V_{\rm DD}$  of 8.5 V and the small signal  $V_{\rm sig}$  was sent to the IC, such that the  $H_3$  was periodically stressed as shown in Fig. 7(b). The capacitor voltage  $V_{\rm CAP}$  was monitored so that the  $V_{\rm TH}$  evolution can be estimated by  $V_{\rm DD}$ - $V_{\rm CAP}$ . Fig. 7 (c) shows that the  $V_{\rm CAP}$  gradually decreased from 6.2 to 5.2 V after 300  $\mu$ s stress, indicating that the  $V_{\rm TH}$  evolved from an initial value of 2.3 V to a stable value of 3.3 V. The saturation time of 300  $\mu$ s is longer than that of the stress  $V_{\rm GS}$  of 3 V in Fig. 3(d), because the initial stress  $V_{\rm GS}$  in Fig. 7 is even lower than 3 V. This test directly demonstrates the evolution of the dynamic  $V_{\rm TH}$  of p-GaN gate HEMTs.

### IV. CONCLUSION

A new methodology of fast sweeping characterization with a short relaxation time of 50 ns has been implemented to characterize the  $V_{\rm TH}$  instability of p-GaN gate HEMTs. The  $V_{\rm TH}$  decrease and  $I_{\rm D}$ - $V_{\rm G}$  hysteresis deterioration are more significant than ever reported, showing that the conventional DC sweeping gives an artificially high  $V_{\rm TH}$  and small hysteresis. PBTI measurements indicate the p-GaN gate has a fast  $V_{\rm TH}$  shifting process and a slower recovery process. The  $V_{\rm TH}$  shifting behaviors however guarantee the stability of p-GaN gate HEMTs in applications after a short initial stress by  $V_{\rm GS}$  of 5 V before circuit shutdown. Nevertheless, the low fresh  $V_{\rm TH}$  at the starting phase can trigger faulty turn-on, which poses a challenge to the gate driver design.

## REFERENCES

- Infineon. (2018). IGO60R070D1 Datasheet. [Online]. Available: https://www.infineon.com

- [2] GaN Systems. (2017). GS66502B Datasheet. [Online]. Available: http://www.gansystems.com

- [3] (2019). Efficient Power Conversion, EPC2019 Datasheet. [Online]. Available: https://epc-co.com/epc

- [4] Y. Xi, M. Chen, K. Nielson, and R. Bell, "Optimization of the drive circuit for enhancement mode power GaN FETs in DC-DC converters," in *Proc. 27th Annu. IEEE Appl. Power Electron. Conf. Exposit. (APEC)*, Feb. 2012, pp. pp. 2467–2471, doi: 10.1109/apec.2012.6166168.

- [5] E. Canato, F. Masin, M. Borga, E. Zanoni, M. Meneghini, G. Meneghesso, A. Stockman, A. Banerjee, and P. Moens, "μs-range evaluation of threshold voltage instabilities of GaN-on-Si HEMTs with p-GaN gate," in *Proc. Int. Rel. Phys. Symp.*, 2019, pp. 1–6, doi: 10.1109/IRPS.2019.8720549.

- [6] A. Stockman, E. Canato, A. Tajalli, M. Meneghini, G. Meneghesso, E. Zanoni, P. Moens, and B. Bakeroot, "On the origin of the leakage current in p-gate AlGaN/GaN HEMTs," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Mar. 2018, pp. 4B–5B, doi: 10.1109/irps.2018. 8353582

- [7] Y. Shi, Q. Zhou, Q. Cheng, P. Wei, L. Zhu, D. Wei, A. Zhang, W. Chen, and B. Zhang, "Bidirectional threshold voltage shift and gate leakage in 650 V p-GaN AlGaN/GaN HEMTs: The role of electron-trapping and hole-injection," in *Proc. IEEE 30th Int. Symp. Power Semicond. Devices ICs (ISPSD)*, May 2018, pp. 96–99, doi: 10.1109/ispsd.2018.8393611.

- [8] A. N. Tallarico, S. Stoffels, N. Posthuma, P. Magnone, D. Marcon, S. Decoutere, E. Sangiorgi, and C. Fiegna, "PBTI in GaN-HEMTs with p-type gate: Role of the aluminum content on ΔV<sub>TH</sub> and underlying degradation mechanisms," *IEEE Trans. Electron Devices*, vol. 65, no. 1, pp. 38–44, Jan. 2018, doi: 10.1109/ted.2017.2769167.

- [9] L. Sayadi, G. Iannaccone, S. Sicre, O. Haberlen, and G. Curatola, "Threshold voltage instability in p-GaN gate AlGaN/GaN HFETs," *IEEE Trans. Electron Devices*, vol. 65, no. 6, pp. 2454–2460, Jun. 2018, doi: 10.1109/ted.2018.2828702.

- [10] X. Tang, B. Li, H. A. Moghadam, P. Tanner, J. Han, and S. Dimitrijev, "Mechanism of threshold voltage shift in p-GaN gate AlGaN/GaN transistors," *IEEE Electron Device Lett.*, vol. 39, no. 8, pp. 1145–1148, Aug. 2018, doi: 10.1109/LED.2018.2847669.

- [11] A. Stockman, E. Canato, M. Meneghini, G. Meneghesso, P. Moens, and B. Bakeroot, "Threshold voltage instability mechanisms in p-GaN gate AlGaN/GaN HEMTs," in *Proc. 31st Int. Symp. Power Semicond. Devices ICs (ISPSD)*, May 2019, pp. 287–290, doi: 10.1109/ispsd.2019.8757667.

- [12] J. He, G. Tang, and K. J. Chen, "V<sub>TH</sub> instability of p-GaN Gate HEMTs under static and dynamic gate stress," *IEEE Electron Device Lett.*, vol. 39, no. 10, pp. 1576–1579, Oct. 2018, doi: 10.1109/led.2018.2867938.

- [13] S. Yang, Y. Lu, H. Wang, S. Liu, C. Liu, and K. J. Chen, "Dynamic gate stress-induced VTH shift and its impact on dynamic RON in GaN MIS-HEMTs," *IEEE Electron Device Lett.*, vol. 37, no. 2, pp. 157–160, Feb. 2016, doi: 10.1109/LED.2015.2505334.

- [14] N. E. Posthuma, S. You, S. Stoffels, H. Liang, M. Zhao, and S. Decoutere, "Gate architecture design for enhancement mode p-GaN gate HEMTs for 200 and 650V applications," in *Proc. IEEE 30th Int. Symp. Power Semicond. Devices ICs (ISPSD)*, May 2018, pp. 188–191, doi: 10.1109/ispsd.2018.8393634.

- [15] X. Li, M. Van Hove, M. Zhao, K. Geens, W. Guo, S. You, S. Stoffels, V.-P. Lempinen, J. Sormunen, G. Groeseneken, and S. Decoutere, "Suppression of the backgating effect of enhancement-mode p-GaN HEMTs on 200-mm GaN-on-SOI for monolithic integration," *IEEE Electron Device Lett.*, vol. 39, no. 7, pp. 999–1002, Jul. 2018, doi: 10.1109/led.2018.2833883.

- [16] X. Li, M. Van Hove, M. Zhao, K. Geens, V.-P. Lempinen, J. Sormunen, G. Groeseneken, and S. Decoutere, "200 V enhancement-mode p-GaN HEMTs fabricated on 200 mm GaN-on-SOI with trench isolation for monolithic integration," *IEEE Electron Device Lett.*, vol. 38, no. 7, pp. 918–921, Jul. 2017, doi: 10.1109/led.2017.2703304.

- [17] O. Hilt, A. Knauer, F. Brunner, E. Bahat-Treidel, and J. Wurfl, "Normally-off AlGaN/GaN HFET with p-type GaN gate and AlGaN buffer," in *Proc. 6th Int. Conf. Integr. Power Electron. Syst.*, 2010, pp. 1–4.

- [18] B. Kaczer, T. Grasser, J. Roussel, J. Martin-Martinez, R. O'connor, B. J. O'sullivan, and G. Groeseneken, "Ubiquitous relaxation in BTI stressing—New evaluation and insights," in *Proc. IEEE Int. Rel. Phys. Symp.*, Apr. 2008, pp. 20–27, doi: 10.1109/relphy.2008.4558858.

- [19] N. É. Posthuma, S. You, H. Liang, N. Ronchi, X. Kang, D. Wellekens, Y. N. Saripalli, and S. Decoutere, "Impact of Mg out-diffusion and activation on the p-GaN gate HEMT device performance," in *Proc. 28th Int. Symp. Power Semicond. Devices ICs (ISPSD)*, Jun. 2016, pp. 95–98, doi: 10.1109/ispsd.2016.7520786.

- [20] W. Götz, N. M. Johnson, D. P. Bour, M. D. Mccluskey, and E. E. Haller, "Local vibrational modes of the Mg-H acceptor complex in GaN," *Appl. Phys. Lett.*, vol. 69, no. 24, pp. 3725–3727, Dec. 1996, doi: 10.1063/1.117202.

- [21] H. Nagai, Q. S. Zhu, Y. Kawaguchi, K. Hiramatsu, and N. Sawaki, "Hole trap levels in Mg-doped GaN grown by metalorganic vapor phase epitaxy," *Appl. Phys. Lett.*, vol. 73, no. 14, pp. 2024–2026, Oct. 1998, doi: 10.1063/1.122356.

- [22] Y. Nakano and T. Jimbo, "Electrical characterization of acceptor levels in Mg-doped GaN," J. Appl. Phys., vol. 92, no. 9, pp. 5590–5592, Nov. 2002, doi: 10.1063/1.1512681.

- [23] L. Sugiura, M. Suzuki, and J. Nishio, "P-type conduction in as-grown Mg-doped GaN grown by metalorganic chemical vapor deposition," *Appl. Phys. Lett.*, vol. 72, no. 14, pp. 1748–1750, Apr. 1998, doi: 10.1063/1.121172.

- [24] W. Götz, N. M. Johnson, and D. P. Bour, "Deep level defects in Mg-doped, p-type GaN grown by metalorganic chemical vapor deposition," *Appl. Phys. Lett.*, vol. 68, no. 24, pp. 3470–3472, Jun. 1996, doi: 10.1063/1.116075.

- [25] X. Li, K. Geens, W. Guo, S. You, M. Zhao, D. Fahle, V. Odnoblyudov, G. Groeseneken, and S. Decoutere, "Demonstration of GaN integrated half-bridge with on-chip drivers on 200-mm engineered substrates," *IEEE Electron Device Lett.*, vol. 40, no. 9, pp. 1499–1502, Sep. 2019, doi: 10.1109/led.2019.2929417.