Contents lists available at ScienceDirect

# Solid State Electronics

journal homepage: www.elsevier.com/locate/sse

# Scaling study of contact operation at constant current in self-aligned top-gated oxide semiconductor field-effect transistors

Yu-Chieh Chien<sup>a,\*,1</sup>, Manoj Nag<sup>a</sup>, Jan Genoe<sup>a,b</sup>, Cedric Rolin<sup>a</sup>

<sup>a</sup> IMEC, Kapeldreef 75, 3001 Leuven, Belgium

<sup>b</sup> KU Leuven, ESAT, B-3001 Leuven, Belgium

# ARTICLE INFO

The review of this paper was arranged by "A. Zaslavsky"

Keywords: Parameter extraction Constant current method Transfer length method Series resistance And contact resistance

## ABSTRACT

An extraction framework that can precisely reflect the metal-semiconductor contact behavior is developed for self-aligned top-gated oxide semiconductor field-effect transistors (SA-TG OS FETs). In contrast to the conventional transfer length method, where the extraction is performed at a constant drain voltage condition, an improved constant current scheme, resilient to bias-dependent series resistance, is employed to enhance the extraction accuracy. This technique enables one to unveil the underlying device physics at the metal-OS interface under top-gated operation. Furthermore, the resistance of contact and extension regions can be accurately differentiated by exploiting the extraction results from the three-terminal FETs and two-terminal resistors using the present framework. Moreover, the significant role of the specific contact resistivity at the metal-OS interface is highlighted as the dominating factor that detrimentally affects the electrical performance of OS FETs.

## 1. Introduction

AMONG different material systems, oxide semiconductors (OS) offer great potential as a semiconducting channel for monolithic integration on silicon complementary metal-oxide-semiconductor (CMOS) technology [1–3]. However, the performance of OS field-effect transistors (FETs) has often been limited by the metal-semiconductor contact, necessitating a comprehensive understanding of their underlying transport mechanism at the metal-OS interface. The contact resistance ( $R_c$ ) and the specific contact resistivity ( $\rho_c$ ) are the essential metrics to evaluate the carrier injection through the metal-semiconductor junction [4]. The accurate determination of  $R_c$  and  $\rho_c$  is non-trivial to elucidate the underlying device physics, practically offering informative insights in optimizing the transistor performance.

The transfer length method (TLM) has been commonly employed to characterize the series resistance ( $R_{SD}$ ), in which a set of FETs with various gate lengths ( $L_g$ ) is needed. Note that the notation of  $R_{SD}$  is used to differentiate from  $R_c$ , as  $R_c$  is a specific parameter that accounts only for the resistance value at the metal-semiconductor junction. In contrast, the  $R_{SD}$  is a generic term that incorporates all the resistance components apart from the channel resistance ( $R_{ch}$ ).

To extract the so-called  $R_{SD}$  from TLM, one has to calculate the total

resistance ( $R_o$ ) to  $L_g$  within the linear regime, and  $R_{SD}$  is determined by extrapolating to the *y*-intercept of the  $R_o$ - $L_g$  plot [4–8]. The above procedure is applicable only when the  $L_g$  measured by scanning electron microscope (SEM) or transmission electron microscope (TEM) matches precisely the effective channel length ( $L_{eff}$ ). This prerequisite is, however, challenging for OS FETs, and the origin can be attributed to i) the deviation created in the photolithography process, ii) the lateral diffusion of hydrogen atoms [9,10], and iii) the creation of oxygen vacancies during the contact-via etching process [11]. Note that the  $R_{SD}$  extraction from the *y*-intercept of the  $R_o$ - $L_g$  plot can be problematic if  $L_g$  differs from  $L_{eff}$ . Alternatively, the convergence point of two adjacent regression lines is taken as the estimated  $R_{SD}$ , and the corresponding length is the difference between  $L_g$  and  $L_{eff}$ . This approach allows one to trace the  $R_{SD}$  and  $L_{eff}$  that evolve with gate voltage ( $V_G$ ) if the extrapolation does not intercept reasonably at the *y*-axis [12–16].

It should be mentioned that the aforementioned methods have mostly adopted a constant drain voltage ( $V_D$ ) scheme, meaning that the calculation of  $R_0$  throughout the whole set of FETs is performed at a fixed  $V_D$  condition (*e.g.*,  $V_D = 0.1$  V) that targets FET operation in the linear regime. We would like to argue that although the constant  $V_D$ setup is intuitive, it is inappropriate to characterize  $R_{SD}$ . In the practical scenario,  $R_{SD}$  is a function of  $V_D$  and  $V_G$ , and the constant  $V_D$  scheme

\* Corresponding author.

https://doi.org/10.1016/j.sse.2022.108406

Received 6 April 2022; Received in revised form 16 June 2022; Accepted 23 June 2022 Available online 25 June 2022 0038-1101/© 2022 Elsevier Ltd. All rights reserved.

E-mail address: yuchieh.chien@u.nus.edu (Y.-C. Chien).

<sup>&</sup>lt;sup>1</sup> Currently with the Department of Electrical and Computer Engineering, National University of Singapore, 4 Engineering Drive 3, 117583 Singapore, Singapore.

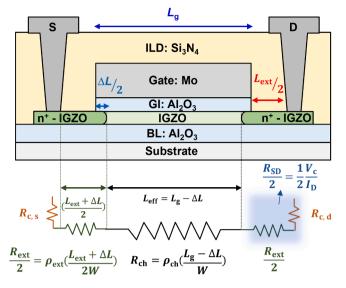

Fig. 1. Schematic and the resistance elements of a SA-TG OS FET.

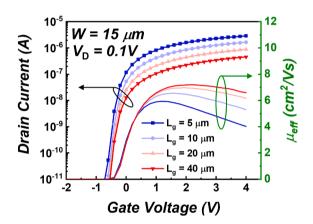

Fig. 2. The  $\mathit{I}_{\rm D}\text{-}\mathit{V}_{\rm G}$  curves and the corresponding  $\mu_{eff}$  of OS FETs with various  $\mathit{L}_g$  at  $\mathit{V}_{\rm D}=0.1$  V.

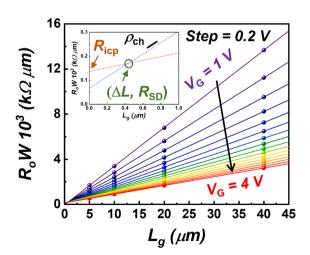

**Fig. 3.**  $R_oW$  versus  $L_g$  plot with  $V_G = 1$  V to  $V_G = 4$  V at  $I_D = 80$  nA. The inset graphically defines the physical interpretation of the convergence point from two adjacent  $V_G$  values.

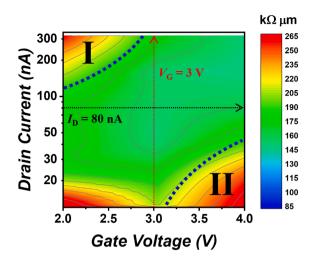

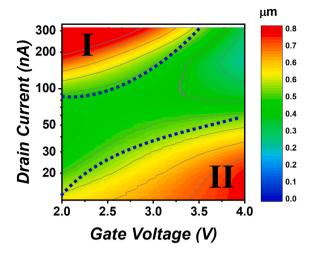

**Fig. 4.** The extracted contour plan of  $R_{SD}$  as a function of  $V_G$  and  $I_D$  with the color scale bar shown in the right side.

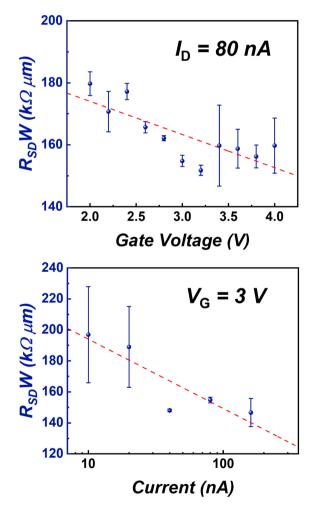

**Fig. 5.** The extracted  $R_{SD}$  from Fig. 4 as a function of (a)  $V_G$  with  $I_D = 80$  nA and (b)  $I_D$  with  $V_G = 3$  V with estimated errors. The corresponding extraction lines are indicated in Fig. 4.

creates an uneven voltage drop across the contact area ( $V_c$ ) for FETs with different  $L_g$ , self-violating the assumption that the bias-dependent  $R_{SD}$  value has to be identical across different  $L_g$  in the extrapolation procedure. For instance,  $V_c$  can be higher in short  $L_g$  (e.g.,  $L_g = 5 \mu$ m) than those with long  $L_g$  (e.g.,  $L_g = 40 \mu$ m) under a fixed  $V_D$  condition. It is,

**Fig. 6.** The extracted contour plan of  $\Delta L$  as a function of  $V_{\rm G}$  and  $I_{\rm D}$  with the color scale bar shown in the right side.

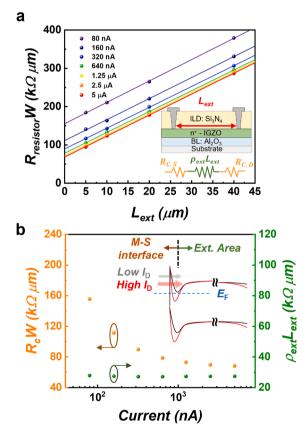

**Fig. 7.** (a)  $R_{\rm resistor}W$ - $L_{\rm ext}$  plot under various  $I_{\rm D}$  from 80 nA to 5  $\mu$ A. Inset shows the schematic of a two-terminal resistor configuration. (b) Extracted  $R_{\rm c}$  and  $R_{\rm ext}$  as a function of  $I_{\rm D}$  with  $L_{\rm ext} = 10 \ \mu$ m. Inset depicts the energy band diagram at the metal-OS interface.

therefore, non-trivial to maintain a constant  $V_c$  to preserve the accuracy of the  $R_{SD}$  extraction [17,18].

Another aspect that has been less explored in self-aligned top-gated (SA-TG) OS FETs is the decomposition of the extracted  $R_{SD}$ . The resistance components of  $R_{SD}$  comprise of  $R_c$  and extension resistance ( $R_{ext}$ ) for a top-gated configuration, as depicted in Fig. 1, where  $\Delta L$  is the channel length deviation caused by channel doping (*e.g.*,  $\Delta L = L_g \cdot L_{eff}$ ). It is argued from the fundamental standpoints that decoupling these resistance elements is pivotal in further optimizing the device

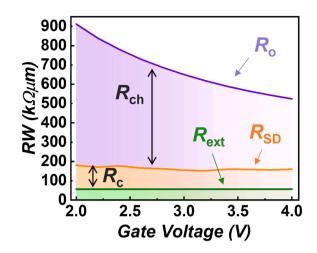

**Fig. 8.** Decomposed  $R_{\rm ch}$ ,  $R_{\rm c}$ , and  $R_{\rm ext}$  as a function of  $V_{\rm G}$  of a  $L_{\rm g} = 5 \,\mu{\rm m}$  OS FET at  $I_{\rm D} = 80$  nA. Green, orange, and purple lines correspond to  $R_{\rm ext}$ ,  $R_{\rm SD}$ , and  $R_{\rm o}$ , respectively. The areas between these lines, from bottom to top, represent  $R_{\rm ext}$ ,  $R_{\rm c}$ , and  $R_{\rm ch}$ , respectively. (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

performance and elucidating the carrier conduction mechanism in SA-TG OS FETs.

In this article, a constant current transfer length method (CC-TLM) is employed to account for the bias-dependent  $R_{SD}$  behavior in the SA-TG OS FETs [17]. We focus on the SA-TG configuration because it manifests substantial potential for fast switching speed due to the negligible parasitic capacitance compared to the bottom-gated counterparts [19,33]. The extraction results show that  $R_{SD}$  can be effectively modulated by the  $V_{\rm G}$  and  $V_{\rm D}$ , whereas a constant  $\Delta L$  value is obtained. The series resistance elements, namely the bias-dependent  $R_c$  and the biasindependent  $R_{\text{ext.}}$  are subsequently differentiated by incorporating the analysis results of using the two-terminal resistors without requiring additional fabrication steps. It should be noted that a systematic analysis of decoupling the resistance components in SA-TG OS FETs is still missing. Our study further suggests that the specific contact resistivity  $(\rho_c)$  is the main obstacle hindering the performance of SA-TG OS FETs, and the  $R_c$  is predominately limited by the available contact length  $(L_{\text{cont}})$ . This work could offer a generic extraction framework to elucidate the underlying contact operation for SA-TG OS FETs, and the extracted parameters may help guide the dimensional design for the devices.

### 2. Experiment

The SA-TG amorphous indium-gallium-zinc oxide (a-InGaZnO) FETs were fabricated, as shown in Fig. 1. The detailed process parameters are described elsewhere [19]. Notably, a 10 nm a-InGaZnO active layer was deposited on a glass substrate with an aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) buffer layer (BL). A 20 nm Al<sub>2</sub>O<sub>3</sub> gate insulator (GI) layer was formed by atomic layer deposition (ALD), followed by gate metal deposition. A 200 nm silicon nitride (Si<sub>3</sub>N<sub>4</sub>) was grown as an interlayer dielectric (ILD). The source/drain (S/D) contacts were formed using 10/50/10 nm titanium/ aluminum/titanium (Ti/Al/Ti) metal layers. Electrical measurements were performed by Agilent 4156C under the ambient condition at room temperature. All the measured OS FETs share identical channel width (W) of 15  $\mu$ m.

In the employed constant current method, the applied  $V_D$  for each FET with different  $L_g$  was automatically adjusted by the source measurement unit (SMU) of the parameter analyzer to adapt for constant current conditions during the  $V_G$  sweep. The voltage compliance at the drain electrode is required to prevent permanent damage (*i.e.*, dielectric breakdown). Note that the adjusted  $V_D$  tends to overshoot when  $V_G$  is adjacent to the threshold voltage ( $V_T$ ) where the  $R_{ch}$  is significant. The

Values Extracted From Os Fet At Different Regimes Of Operation.

| I <sub>D</sub> (nA) | $\rho_{\rm c}~(\Omega {\rm cm}^2)$ | $ρ_{\rm ext}$ (kΩ/□) | $ρ_{\rm ch}$ (kΩ/□) | $R_{\rm c}~(k\Omega\mu m)$ | $R_{\rm ext} (k\Omega\mu m)$ | $R_{\rm ch}~(k\Omega\mu m)$ | $L_{\rm T}$ (µm) | $\Delta L$ (µm) | $L_{\rm cont}~(\mu m)$ | $L_{\rm ext}$ ( $\mu m$ ) | <i>L</i> g (μm) | W (µm) |

|---------------------|------------------------------------|----------------------|---------------------|----------------------------|------------------------------|-----------------------------|------------------|-----------------|------------------------|---------------------------|-----------------|--------|

| 20                  | N/A                                | N/A                  | 77.25               | N/A                        | N/A                          | 354.58                      | N/A              | 0.41            | 5                      | 10                        | 5               | 15     |

| 80                  | $3.73\times10^{-3}$                | 5.58                 | 77.18               | 103.15                     | 58.16                        | 352.71                      | 13.95            | 0.43            | 5                      | 10                        | 5               | 15     |

| 320                 | $2.24\times10^{-3}$                | 5.43                 | 77.68               | 90.12                      | 56.61                        | 355.77                      | 8.25             | 0.42            | 5                      | 10                        | 5               | 15     |

Not applicable (*N*/*A*).  $\rho_{ch}$ ,  $R_c$ , and  $R_{ch}$  are calculated at  $V_G = 4$  V.

constant current conditions are carefully selected and monitored to ensure that the applied  $V_D$  resides within the linear regime ( $V_G$ - $V_T \gg V_D$ ) throughout the entire extraction region (*e.g.*,  $V_G = 2$  V to 4 V) for different  $L_g$ . The overloaded  $V_D$  with high input current (*e.g.*,  $V_G$ - $V_T \leq$  $V_D$ ) should be excluded as the measured FETs consequently operate in the saturation regime that is not applicable to the present technique.

#### 3. Improved constant current method

Fig. 2 shows the transfer characteristics  $(I_D-V_G)$  and the effective mobility ( $\mu_{eff}$ ) with various  $L_g$  at  $V_D = 0.1$  V.  $\mu_{eff}$  is calculated by the transconductance method ( $g_m$ ) as.

$$\mu_{\rm eff} = \frac{g_{\rm m} L_{\rm g}}{W C_{\rm ox} V_{\rm D}} \tag{1}$$

where  $g_m$  is defined as  $\partial I_D / \partial V_G$ , *W* is the channel width, and  $C_{ox}$  is the oxide capacitance per unit area determined by the capacitance-voltage (*C-V*) measurement. Note that the  $g_m$  method has been considerably employed in the literature to determine the mobility in FETs, despite the substantial flaw of this technique [4].

On the other hand, the TLM can separately extract  $R_{\rm SD}$  and intrinsic charge carrier mobility ( $\mu_{\rm int}$ ) from the  $I_{\rm D}$ - $V_{\rm G}$  curves with different  $L_{\rm g}$ . This technique presumes that the contact and channel properties are identical across the tested devices in which a linear extrapolation is performed to extract the parameters. The measurements are typically conducted under a constant  $V_{\rm D}$  condition (e.g.,  $V_{\rm D} = 0.1$  V) that implicitly assumes an ideal ohmic contact behavior. This assumption, however, oversimplifies the practical scenario since carrier injection generally shows non-trivial bias dependence [4,20]. Furthermore, the constant  $V_{\rm D}$  condition substantially varies the voltage drop across the contacts for FETs with different  $L_{\rm g}$  and thus makes the extracted  $R_{\rm SD}$ dubious.

Therefore, the CC-TLM is employed to mitigate the errors created by the conventional approach, where a consistent voltage drop across the contact regions is ensured for all channel lengths [17]. The applied  $V_D$  is automatically adjusted to achieve the constant current conditions throughout the  $V_G$  sweep for FETs with different  $L_g$ . Fig. 3 shows the  $R_o$ - $L_g$  plots under various  $V_G$  from 1 V to 4 V at the constant current ( $I_D$ ) of 80 nA. All the measured OS FETs operate in the linear regime in such conditions, and a reasonable linear extrapolation can be attained under the entire  $V_G$  sweep. The total resistance,  $R_o$ , is written as.

$$R_{\rm o}W = R_{\rm SD}W + \rho_{\rm ch}(L_{\rm g} - \Delta L) \tag{2}$$

$\rho_{ch}$  is the channel sheet resistance. Accordingly, the  $R_{SD}$  and  $\Delta L$  can be extracted from the convergence point of the  $R_0$ - $L_g$  plots between two adjacent  $V_G$  values, as indicated in the inset of Fig. 3 [12–16,21,22].

The constant current levels are subsequently varied from 10 nA to 320 nA to explore the carrier injection behavior in OS FETs. The contour plan of the extracted  $R_{SD}$  as a function of  $V_G$  and  $I_D$  conditions is shown in Fig. 4, which manifests that the  $R_{SD}$  can be effectively modulated by the measured conditions. More specifically, the extracted  $R_{SD}$  decreases with both the gate and drain biases, as shown in Fig. 5 (a) and (b), respectively, evidencing the non-ohmic behavior of charge transport in the non-channel region. Notably, the extracted  $R_{SD}$  shows less  $V_G$  dependency than  $I_D$  (*e.g.*, different  $I_D$  at identical  $V_G$ ), which can be attributed to the SA-TG configuration. The absence of direct overlapping of gate and contact electrodes makes the modulation of  $R_{SD}$  by  $V_G$  less

effective than FETs with a staggered configuration. Nevertheless, the observation further highlights the deficiency of the conventional constant  $V_{\rm D}$  method that neglects the  $V_{\rm D}$ -dependent  $R_{\rm SD}$ .

It should be noted that the prominent extraction errors observed in the region I of Fig. 4 can be attributed to the unfulfillment of the linear condition ( $V_{\rm G}$ - $V_{\rm T} \gg V_{\rm D}$ ) in long channel FETs. The applied  $V_{\rm D}$  for the long channel FET (e.g.,  $L_g = 40 \ \mu m$ ) has to be increased at small  $V_G$ conditions to achieve the identical  $I_{\rm D}$  as of the short channel FET (e.g.,  $L_{\rm g}$ = 5  $\mu$ m), inevitably introducing errors in the R<sub>SD</sub> extraction. For instance, a  $V_D$  of 0.15 V is supplied to achieve a  $I_D$  of 300 nA with  $L_g =$ 40  $\mu$ m, and the gate overdrive ( $V_{OV} = V_G - V_T$ ) at  $V_G = 2$  V is calculated as  $\sim$  1 V ( $V_{\rm T}$   $\sim$  1 V in Fig. 2). Note that the quantitative criteria to ensure a linear-region operation is defined as  $(V_{\rm G}-V_{\rm T})/m$ , where *m* is a constant that describes the voltage transfer efficiency to the surface potential,  $\psi_s$ , as  $d\psi s/dV_G = 1 + (C_{os}/C_{ox}) + (C_{it}/C_{ox})$  [23]. The  $C_{os}$  and  $C_{it}$  denote the semiconductor and interface trap capacitances, respectively. Assuming the relative dielectric constant of the oxide semiconductor and Al<sub>2</sub>O<sub>3</sub> as 16 and 8, respectively, and the interface trap density ( $D_{it} = q^{-1}C_{it}$ ) of ~  $10^{12} \text{ eV}^{-1} \text{cm}^{-2}$ , the *m* of ~ 5.5 can be calculated [24]. Consequently, the criteria of  $(V_{\rm G}-V_{\rm T})/m$  at  $V_{\rm G} = 2$  V becomes 0.18, similar to the applied  $V_{\rm D}$ condition ( $V_{\rm D} = 0.15$  V) to achieve a  $I_{\rm D}$  of 300 nA for devices with  $L_{\rm g} =$ 40 µm. In other words, the linear region operation (e.g.,  $V_{\rm G}$ - $V_{\rm T} \gg V_{\rm D}$ ) cannot be firmly ensured for  $L_g = 40 \ \mu m$  at the aforementioned condition, and thus potentially introducing the error during extraction.

On the other hand, the extracted  $R_{\rm SD}$  deviates in region II, where a large  $V_{\rm G}$  is applied (*i.e.*,  $V_{\rm G} > 3.5$  V), as the corresponding  $V_{\rm D}$  is very low and exhibits considerable fluctuation. For instance, a  $V_{\rm D}$  of  $\sim 300 \ \mu$ V is applied to supply a  $I_{\rm D}$  of 10 nA for devices with  $L_{\rm g} = 5 \ \mu$ m. However, this applied  $V_{\rm D}$  condition is approaching the resolution limit of our SMUs (*e. g.*,  $\sim 100 \ \mu$ V). Thus, the extraction within this region could be unreliable and is susceptible to measurement noises. One should note that it is practically challenging to define precisely the extraction margin of regions I and II, so the drawn lines are, strictly speaking, only applicable to guide the eye. Nevertheless, the bias-dependent  $R_{\rm SD}$  behavior shown in Fig. 4 demonstrates that the present method is capable of capturing the detailed mechanism of the carrier conduction in OS FETs.

Additionally, Leff is an essential aspect in evaluating the process technology. To this end,  $\Delta L$  is extracted in which the contour plan is created in Fig. 6. The extracted  $\Delta L$  virtually exhibits an independent behavior of  $V_{\rm G}$  and  $I_{\rm D}$  within the reliable measurement conditions (see the blue dash lines in Fig. 6). The extraction results in region I and II are not included in the discussion due to the inherent errors mentioned in the above paragraph. However, the extraction of  $\Delta L$  shows a broader error window than the extracted R<sub>SD</sub>. (*i.e.*, region II in Fig. 4 and Fig. 6). Note that the  $\Delta L$  values are calculated from the slope of the  $R_{\rm icp}$ - $\rho_{\rm ch}$ curves from two adjacent  $V_{\rm G}$  biases, in which  $R_{\rm icp}$  and  $\rho_{\rm ch}$  are the fitted yintercept and slope of the  $R_0$ - $L_g$  plot, respectively (see Fig. 3) [21,22]. One plausible explanation is that a slight deviation from the extracted  $R_{\rm icp}$  and  $\rho_{\rm ch}$  could substantially raise the uncertainty in determining  $\Delta L$ , given that the first derivative is highly sensitive to errors. In OS FETs,  $\Delta L$ could be caused by hydrogen originating from the interlayer dielectric layer that diffuses inwards in the channel under the top gate electrode. Indeed, hydrogen atoms act as an n-type dopant for the OS layer that can degenerate the underlying extension region [9,10,25-27]. The values of  $\Delta L$  remain in the low range ( $\Delta L \sim 0.4 \ \mu m$ ) of previously published values ( $\Delta L > 1.0 \ \mu$ m) with silicon dioxide (SiO<sub>2</sub>) GI, implying that the low-temperature ALD Al<sub>2</sub>O<sub>3</sub> could be a suitable diffusion barrier against hydrogen atoms [9,10,14-16].

#### 4. Series resistance decomposition

Although the  $R_{SD}$  has been characterized in the above section, the resistance components of  $R_{SD}$  remain unclear. It is, however, imperative to decouple them to further elucidate the underlying device physics. The  $R_{SD}$  comprises of the  $R_c$  and  $R_{ext}$  as.

$$R_{\rm SD} = R_{\rm c} + R_{\rm ext} \tag{3}$$

The parasitic metal resistance ( $R_m$ ) is neglected in (3), which can be justified by the subsequent extraction results of  $\rho_c$  (*e.g.*,  $R_c \gg R_m$ ), showing a negligible contribution from  $R_m$ . Note that  $R_c$  is equivalent to the contact-front resistance in the transmission line theory [4]. A set of two-terminal resistors [see the inset of Fig. 7 (a)] with different lengths is employed to decompose the resistances listed in (3) using the constant current scheme. Such two-terminal configurations are useful for the precise characterization of OS FETs and can be easily integrated as they do not require additional photolithography steps. The resistance of the measured resistors ( $R_{resistor}$ ) can be written as.

$$R_{\text{resistor}}W = R_{c}W + \rho_{\text{ext}}L_{\text{ext}}$$

(4)

Where  $\rho_{\text{ext}}$  and  $L_{\text{ext}}$  are the sheet resistance and length of the extension region, respectively. To extract  $R_{\text{c}}$  and  $\rho_{\text{ext}}$ ,  $R_{\text{resistor}}$  with various  $L_{\text{ext}}$  is plotted under different current conditions, as shown in Fig. 7 (a). Good linear regression can be acquired from the current level of 80 nA to 5  $\mu$ A, indicating that the  $R_{\text{c}}$  and  $\rho_{\text{ext}}$  can be reliably extracted from the *y*-intercept and slope of (4), respectively. Note that a higher current range is selected than the FET measurements, as a sufficiently large current is needed to produce a stable voltage signal in the resistor configuration due to its high conductivity.

The extracted  $R_c$  and  $R_{ext}$  as a function of current are shown in Fig. 7 (b). One can clearly observe that  $R_c$  decreases with the input current, whereas the  $R_{ext}$  exhibits a current-independent behavior. The above results can be explained by the inset of Fig. 7 (b), in which a Schottky-like metal-OS contact is responsible for the observed current-dependent  $R_c$ . Subsequently, the carriers conduct through the metallic-like ohmic extension region.

Moreover, Fig. 7 allows one to estimate the  $\rho_c$  at the metalsemiconductor interface by the transmission line theory, considering the current crowding effect as.

$$R_{\rm c}W = \rho_{\rm c}/L_{\rm T} coth(L_{\rm cont}/L_{\rm T})$$

(5a)

$$\approx \rho_{\rm c}/L_{\rm T}$$

when  $1.5L_{\rm T} \le L_{\rm cont}$  (5b)

$$\approx \rho_{\rm c} / L_{\rm cont} when 0.5 L_{\rm T} \ge L_{\rm cont}$$

(5c)

$L_{\rm cont}$  and  $L_{\rm T}$  denote the contact and transfer length [4,28,30]. By assuming that the sheet resistances in both the extension ( $\rho_{sh,ext}$ ) and contact ( $\rho_{sh c}$ ) regions are identical, one can estimate  $L_T$  of 13.95 µm and 8.25  $\mu$ m from the x-intercept of Fig. 7 (b) at the current level of 80 nA and 320 nA, respectively. These estimated values are prominently higher than  $L_{\text{cont}}$  (=5 µm). In consequence, the hyperbolic cotangent term in (5a) can be simplified, and  $\rho_c$  is extracted from (5c), which is insensitive to the error arising from the determination of  $L_{\rm T}$ . This yields  $\rho_{\rm c}$  of 3.73  $\times$  10<sup>-3</sup>  $\Omega$ cm<sup>2</sup> and 2.24  $\times$  10<sup>-3</sup>  $\Omega$ cm<sup>2</sup> at the current level of 80 nA and 320 nA, respectively. These values are at least five orders higher than the silicon technology ( $\sim 10^{-9} \ \Omega \text{cm}^2$ ), which urgently requires considerable improvement [31,32]. Note that the extracted  $\rho_{\rm c}$  at  $I_D=80$ nA can be justified by fulfilling  $0.5L_{\rm T} \ge L_{\rm cont}$ , whereas the  $\rho_{\rm c}$  value from  $I_{\rm D}=320$  nA is a rough approximation. To accurately and comprehensively determine the  $\rho_c$  values at different current levels, it is necessary to adopt other approaches, such as the contact-end measurement [4,29,30].

As a final step, the resistive elements present in the FET are decomposed at a constant current of  $I_{\rm D} = 80$  nA, as shown in Fig. 8 for an

OS FET of  $L_g = 5 \,\mu$ m. In this graph,  $R_{\text{ext}}$  is calculated from the  $\rho_{\text{ext}}$  value obtained from the two-terminal resistor multiplied by  $L_{\text{ext}} + \Delta L$ .  $R_{\text{ch}}$  is calculated from channel sheet resistivity  $\rho_{\text{ch}}$  obtained from the TLM analysis multiplied by  $L_{\text{g}}$ - $\Delta L$ . Finally,  $R_{\text{c}}$  is obtained from (3), using the  $R_{\text{SD}}$  values extracted from CC-TLM analysis. Table 1 summarizes the extracted values of various resistive elements from different constant current conditions. Fig. 8 shows unambiguously that  $R_{\text{c}}$  occupies most of the resistance portion in  $R_{\text{SD}}$  ( $R_{\text{c}}/R_{\text{SD}} \sim 65$  %), hindering the device performance of the OS FETs. When increasing  $V_{\text{G}}$ ,  $R_{\text{SD}}$  expectedly rises to nearly half of  $R_{\text{ch}}$  at  $V_{\text{G}} = 4$  V. It is clear that further downscaling of channel and extension lengths would result in a contact-dominated device as  $R_{\text{c}}$  would only rise if  $L_{\text{cont}}$  is downscaled along with the other FET dimensions.

It should be noted that the aforementioned discussion can only be conducted if one employs the concept of CC-TLM [17] on both three-terminal FETs and two-terminal resistors and in conjunction with Ter-ada's method to extrapolate  $R_{\rm SD}$  and  $\Delta L$  [12]. Furthermore, the analysis stresses the importance of developing strategies to minimize  $R_{\rm c}$  ( $\rho_{\rm c}$ ) at the metal-OS interface to benefit from the effort spent on downscaling the SA-TG OS FETs configuration in the sub-µm range (*i.e.*,  $L_{\rm g} \sim 0.1$  µm).

## 5. Conclusion

An improved methodology was exploited to accurately account for the bias-dependent  $R_{\rm SD}$  in the SA-TG OS FETs. Indeed, the extraction results demonstrated that the  $R_{\rm SD}$  can be effectively modulated by both the  $V_{\rm G}$  and  $V_{\rm D}$ , validating the applicability of the present technique for SA-TG OS FETs. Additionally, a two-terminal resistor configuration was employed to precisely differentiate the resistance elements of  $R_{\rm SD}$ . This study highlighted that the substantial  $\rho_{\rm c}$  is the dominating factor that considerably limits the device performance of OS FETs. More importantly, the presented analyses could offer a systematic extraction framework to clarify the underlying mechanisms for SA-TG OS FETs, which is practically indispensable to further enhance their electrical performance.

#### **Declaration of Competing Interest**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

### References

- Nomura K, Ohta H, Takagi A, Kamiya T, Hirano M, Hosono H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004;432(7016):488–92.

- [2] Onuki T, Uesugi W, Isobe A, Ando Y, Okamoto S, Kato K, et al. Embedded Memory and ARM Cortex-M0 Core Using 60-nm C-Axis Aligned Crystalline Indium-Gallium-Zinc Oxide FET Integrated with 65-nm Si CMOS. IEEE J Solid-State Circuits 2017; 52(4):925–32.

- [3] Ishizu T, et al. A 140 MHz 1 Mbit 2T1C Gain-Cell Memory with 60-nm Indium-Gallium-Zinc-Oxide Transistor Embedded into 65-nm CMOS Logic Process Technology. In: Symposium on VLSI Circuits Dig. Tech.; 2017. C162–3.

- [4] Schroder Dieter K. Semiconductor Material and Device Characterization. Ch. 3. 3rd ed. Weinheim, Germany: Wiley-VCH; 2006.

- [5] Kim H, Kim K-K, Lee S-N, Ryou J-H, Dupuis RD. Low resistance Ti/Au contacts to amorphous gallium indium zinc oxides. Appl Phys Lett 2011;98(11):18–21.

- [6] Wang W, Li L, Lu C, Liu Yu, Lv H, Xu G, et al. Analysis of the contact resistance in amorphous InGaZnO thin film transistors. Appl Phys Lett 2015;107(6):063504.

- [7] Uemura T, Rolin C, Ke T-H, Fesenko P, Genoe J, Heremans P, et al. On the Extraction of Charge Carrier Mobility in High-Mobility Organic Transistors. Adv Mater 2016;28(1):151–5.

- [8] Xu Y, Li Y, Li S, Balestra F, Ghibaudo G, Li W, et al. Precise Extraction of Charge Carrier Mobility for Organic Transistors. Adv Funct Mater 2020;30(20):1904508.

- [9] Chen H-C, et al. Hydrogen Diffusion and Threshold Voltage Shifts in Top-Gate Amorphous InGaZnO Thin Film Transistors. IEEE Trans Electron Devices Aug. 2020;67(8):3123–8.

- [10] Kim HW, Kim ES, Park JS, Lim JH, Kim BS. Influence of effective channel length in self-aligned coplanar amorphous-indium-gallium-zinc-oxide thin-film transistors with different annealing temperatures. Appl Phys Lett 2018;113(2):022104.

#### Y.-C. Chien et al.

- [11] Yang C-I, Tsai C-M, Yu M-C, Zhang S, Chang T-C, Liao P-Y, et al. Drain-Induced-Barrier-Lowing-Like Effect Induced by Oxygen-Vacancy in Scaling-Down via-Contact Type Amorphous InGaZnO Thin-Film Transistors. IEEE J Electron Devices Soc 2018;6:685–90.

- [12] Terada K, Muta H. A New Method to Determine Effective MOSFET Channel Length. Jpn J Appl Phys 1979;18(5):953–9.

- [13] Chern JGJ, Chang P, Motta RF. A New Method to Determine MOS Channel Length. IEEE Electron Dev Lett 1980;(9):170–3.

- [14] Oh H, Pi J-E, Hwang C-S, Kwon O-S. Impact of SiN x capping on the formation of source/drain contact for In-Ga-Zn-O thin film transistor with self-aligned gate. Appl Phys Lett 2017;111(25):253504.

- [15] Liang T, Shao Y, Lu H, Zhou X, Deng X, Zhang S. Scalability and Stability Enhancement in Self-Aligned Top-Gate Indium- Zinc-Oxide TFTs with Al Reacted Source/Drain. IEEE J Electron Devices Soc 2018;6(May):680–4.

- [16] Hong S-Y, Kim H-J, Kim D-H, Jeong H-Y, Song S-H, Cho I-T, et al. Study on the Lateral Carrier Diffusion and Source-Drain Series Resistance in Self-Aligned Top-Gate Coplanar InGaZnO Thin-Film Transistors. Sci Rep 2019;9(1).

- [17] Yang J-G, Seah W-L, Guo H, Tan J-K, Zhou Mi, Matsubara R, et al. Characterization of ohmic contacts in polymer organic field-effect transistors. Org Electron 2016;37: 491–7.

- [18] Rolin C, et al. Contact resistance characterization in organic thin film transistors (Conference Presentation. Organic Field-Effect Transistors XVII 2018;10739: 107390R.

- [19] Chien YC, et al. Origin of High Current and Illumination Stress Instability in Self-Aligned a-InGaZnO Thin Film Transistors With Al<sub>2</sub>O<sub>3</sub> as High- κ Gate Dielectric. IEEE Trans Electron Devices 2020;41(4):565–8.

- [20] Sze SM, Ng KK. Physics of semiconductor devices. 3rd ed. Wiley Online Library; 2007.

- [21] Liu C, Xu Y, Ghibaudo G, Lu X, Minari T, Noh Y-Y. Evaluating injection and transport properties of organic field-effect transistors by the convergence point in transfer-length method. Appl Phys Lett 2014;104(1).

- [22] Chien YC, et al. An Analytical Method for Parameter Extraction in Oxide Semiconductor Field-Effect Transistors. IEEE Trans Electron Devices 2021;68(6): 2717–22.

- [23] Taur Y, Ning TH. Fundamentals of Modern VLSI Devices. 2nd ed. Cambridge University Express; 2009.

- [24] Li Y, Pei YL, Hu RQ, Chen ZM, Zhao Y, Shen Z, et al. Effect of channel thickness on electrical performance of amorphous IGZO thin-film transistor with atomic layer deposited alumina oxide dielectric. Curr Appl Phys 2014;14(7):941–5.

- [25] Chien Y-C, et al. Hydrogen as a Cause of Abnormal Subchannel Formation Under Positive Bias Temperature Stress in a-InGaZnO Thin-Film Transistors. IEEE Trans Electron Dev 2019;66(7):2954–9.

- [26] Kang Y, Ahn BD, Song JH, Mo YG, Nahm H-H, Han S, et al. Hydrogen Bistability as the Origin of Photo-Bias-Thermal Instabilities in Amorphous Oxide Semiconductors. Adv Electron Mater 2015;1(7):1400006.

- [27] Van de Walle CG. Hydrogen as a cause of doping in zinc oxide. Phys Rev Lett Jul. 2000;85(5):1012–5.

- [28] Berger HH. Models for Contacts to Planar Devices. Solid State Electron June 1971; 15(2):145–58.

- [29] Reeves GK, Harrison HB. Obtaining the specific contact resistance from transmission line model measurements. IEEE Electron Device Lett May 1982;3(5): 111–3.

- [30] Cohen SS, Gildenbalt GS. Metal-Semiconductor Contacts and Devices. Ch. 4. 1st ed. Elsevier; 1986.

- [31] Yu H, Schaekers M, Schram T, Rosseel E, Martens K, Demuynck S, et al. Multiring Circular Transmission Line Model for Ultralow Contact Resistivity Extraction. IEEE Electron Dev Lett 2015;36(6):600–2.

- [32] Ni C-N, et al. Ultra-Low Contact Resistivity with Highly Doped Si:P Contact for nMOSFET. In: Symposium on VLSI Circuits Dig. Tech.; 2015. T118–9.

- [33] Kang DH, Kang I, Ryu SH, Jiang J. Self-Aligned Coplanar a-IGZO TFTs and Application to High-Speed Circuits. IEEE Electron Dev Lett 2011;32(10):1385–7.

Yu-Chieh Chien is currently pursuing his Ph.D. degree with the Department of Electrical & Computer Engineering, National University of Singapore (NUS), Singapore. He received his B.S. degree with the Department of Materials and Optoelectronic Science, National Sun Yat-Sen University (NSYSU), Taiwan, in 2018.

Prior to his move to NUS, he was an international scholar at the Department of Large Area Electronics, Imec, Belgium and the KU Leuven, Belgium, where he was working on the electrical characterizations of oxide semiconductors with the focus on parameter extractions and bias temperature instability issues.

His current research interest includes oxide semiconductors, III-V materials, and two-dimensional semiconductors with the focus on the field-effect transistors.