# ESD HBM Discharge Model in RF GaN-on-Si (MIS)HEMTs

Wei-Min Wu<sup>®</sup>, Ming-Dou Ker<sup>®</sup>, Fellow, IEEE, Shih-Hung Chen<sup>®</sup>, Senior Member, IEEE, Arturo Sibaja-Hernandez<sup>®</sup>, Sachin Yadav, Uthayasankaran Peralagu<sup>®</sup>, Hao Yu<sup>®</sup>, Member, IEEE, AliReza Alian, Vamsi Putcha<sup>®</sup>, Bertrand Parvais<sup>®</sup>, Nadine Collaert, Member, IEEE, and Guido Groeseneken<sup>®</sup>, Fellow, IEEE

Abstract -- Gallium nitride (GaN) technologies have become an essential role in commercial advanced RF systems, which accompany emerging RF electrostatic discharge (ESD) reliability challenges. As opposed to ESD clamp transistors in LV CMOS technologies, a mis-correlation between standard-defined human body model (HBM) ESD robustness and commonly used TLP failure current was observed in GaN (MIS) high electron mobility transistors (HEMTs). Using transient HBM LV characteristics, a novel discharge model is proposed to explain the transient discharge mechanism. The TCAD and SPICE simulations confirmed that the observed mis-correlation between TLP and HBM is attributed to 2-dimensional electron gas (2DEG) resistance modulation in response to HBM ESD transient voltage waveforms. The HBM waveforms under full transient duration in terms of rising and falling edges are further discussed. Eventually, the failure mechanisms in the TLP IVs and the HBM transient IVs can be well correlated in GaN (MIS)HEMTs.

Index Terms— Electrostatic discharge (ESD), gallium nitride (GaN), high electron mobility transistor (HEMT), human body model (HBM), radio frequency (RF).

# I. Introduction

ALLIUM nitride (GaN)-on-Si technology with 3-D monolithic heterogeneous integration technique is a

Manuscript received November 8, 2021; revised December 23, 2021; accepted January 3, 2022. Date of publication January 25, 2022; date of current version March 28, 2022. This work was supported in part by the Ministry of Science and Technology (MOST), Taiwan, under Contract MOST 110-2622-8-009-017-TP1. This article is an extended version of a paper presented at IEDM 2021. The review of this article was arranged by Editor G. Meneghesso. (Corresponding author: Ming-Dou Ker.)

Wei-Min Wu is with the Institute of Electronics, National Yang Ming Chiao Tung University, Hsinchu 300, Taiwan, also with the IMEC, 3001 Leuven, Belgium, and also with the ESAT Department, Katholieke Universiteit Leuven, 3001 Leuven, Belgium (e-mail: sam199208.ee05@nycu.edu.tw).

Ming-Dou Ker is with the Institute of Electronics, National Yang Ming Chiao Tung University, Hsinchu 300, Taiwan (e-mail: mdker@ieee.org). Shih-Hung Chen, Arturo Sibaja-Hernandez, Sachin Yadav, Uthayasankaran Peralagu, Hao Yu, AliReza Alian, Vamsi Putcha, and Nadine Collaert are with the IMEC, 3001 Leuven, Belgium.

Bertrand Parvais is with the IMEC, 3001 Leuven, Belgium, and also with the Department of Electronics and Informatics, Vrije Universiteit Brussels, 1050 Ixelles, Belgium.

Guido Groeseneken is with the IMEC, 3001 Leuven, Belgium, and also with the ESAT Department, Katholieke Universiteit Leuven, 3001 Leuven, Belgium.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2022.3141038.

Digital Object Identifier 10.1109/TED.2022.3141038

promising candidate to enable the low cost and optimal high performant RF/mmWave front-end modules (FEM) in 5G applications [1], [2]. Wide bandgap with high electric field breakdown [3], high electron mobility [4], and high saturation velocity [5], [6] in 2-dimensional electron gas (2DEG) channel of the GaN high electron mobility transistors (HEMTs) provide superior lateral breakdown voltage and output power in RF/mmWave power amplifier (PA) designs [7]. Currently, the RF GaN transistor technology is mainly based on the Schottky HEMT. However, the GaN Schottky HEMTs suffer from high gate leakage due to the metal-semiconductor gate structures, which has an impact on the power-added efficiency (PAE) of the PA [8]. Thus, metal-insulator-semiconductor MIS-HEMTs [9], [10] are proposed to alleviate the gate leakage issue. In spite of the advantages of these GaN devices, they are known to suffer from well-studied reliability concerns, such as ON-resistance  $(R_{ON})$  dispersion [11]–[13], time-dependent dielectric breakdown (TDDB) [14], [15], bias temperature instability (BTI), and hot carrier degradation (HCD) [16]–[18]. However, the investigations of the electrostatic discharge (ESD) reliability of RF GaN technology are still in a nascent

A 50- $\Omega$  transmission line pulse (TLP) tester is commonly used to investigate device IV characteristics under a hundred-nanosecond ESD-like transient duration in the CMOS IC industry [19]. The previously reported ESD studies of GaN-based Schottky diodes [20] and (MIS)HEMTs [21]-[24] were evaluated by  $50-\Omega$  TLP testers. In [21], additional DC experiments on transconductance  $(g_m)$ , OFF-state drain current  $(I_D)$ , and gate-to-source current  $(I_{GS})$  are essential to obtain an accurate failure current  $(I_{t2})$  in the TLP I-Vcharacteristics. Once the gate biases were applied to define the ON-state and OFF-state stress conditions in TLP experiments, the corresponding failure mechanism was revealed. The ON-state failures belong to power-dependent failures, whereas the OFF-state failures are electric-field-dependent failures in accordance with the failure analysis (FA) [22]. A more detailed analysis of ESD TLP failures in HEMT devices combined with the piezoelectric field, carrier trapping, and self-heating effects were studied [23]. Besides, ESD failure comparisons of RF MIS-HEMTs and HEMTs were primarily discussed in [24]. Although the  $50-\Omega$  TLP results can provide the device failure current levels, the commercial human body model (HBM) ESD robustness had been rarely certified in any of the prior

0018-9383 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

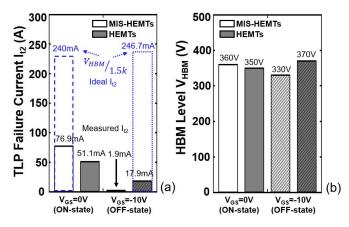

Fig. 1. (a) Measured TLP  $I_2$ , and (b) measured HBM robustness ( $V_{\rm HBM}$ ) in GaN MIS-HEMTs and HEMTs at ON-state and OFF-state comparison. All the measured TLP  $I_2$  have mis-correlation issue to the measured  $V_{\rm HBM}$ . The ideal  $I_2$  values which can use 1.5 k $\Omega$  factor are illustrated by blue columns. For ON-state stress, the TLP  $I_2$  are limited by channel driving capability in saturation region, whereas for OFF-state stress, the TLP  $I_2$  are the channel leakage of the devices, which causes worse correlation [24].

works [21]–[23]. Our previous work [24] has disclosed that the  $I_{t2}$  from 50- $\Omega$  TLP cannot be directly correlated with the standard-defined HBM robustness by the empirical correlation ( $V_{\text{HBM}} = I_{t2} \times \sim 1.5 \text{ k}\Omega$ ). The results are depicted in Fig. 1.

In this article, in-depth investigations of the HBM discharge physical mechanism in RF GaN (MIS)HEMTs are conducted. Transient HBM I-V characteristics [25], [26] are used to propose a new transient discharge model, with a novel resistance modulation, which can successfully describe the transient discharge mechanism in the GaN (MIS)HEMTs. Moreover, the root cause of the mis-correlation between the TLP  $I_{t2}$  and HBM ESD robustness in the RF GaN (MIS)HEMTs is fundamentally linked to the discrepancy between LV CMOS technologies and RF GaN technologies. Finally, the updated correlation between TLP I-V and HBM I-V characteristics of GaN (MIS)HEMTs can be proposed and shown in this article.

# II. RF GAN-ON-SI (MIS)HEMT TECHNOLOGY

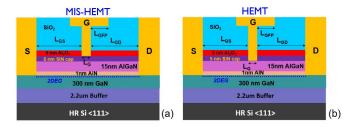

The MIS-HEMT and HEMT device structures are manufactured in 200 mm GaN-on-Si wafers [27]. A 2.2  $\mu$ m GaN-based buffer, a 300 nm GaN channel, a 1 nm AlN spacer, and a 15 nm AlGaN barrier are grown sequentially on a high-resistivity Si (111) substrate and capped *in situ* with 5 nm SiN. An additional Al<sub>2</sub>O<sub>3</sub> layer is deposited before the follow-up of the S–D formations. The *T*-shaped gate structure is made of a metal stack of 40 nm TiN/20 nm Ti/250 nm AlCu/20 nm Ti/60 nm TiN, such that the length of field plate metal toward the drain contact can be varied. The gate metal stack is deposited on the SiN capping layer in MIS-HEMTs directly, whereas the SiN layer in the channel region is etched out before depositing the gate metal in the case of HEMTs (to form a Schottky contact), as shown in Fig. 2(a) and (b). The geometric sizes in the experiments are fixed at  $W = 100 \ \mu$ m,

Fig. 2. Cross-sectional views of GaN-on-Si (a) MIS-HEMT and (b) HEMT [27].

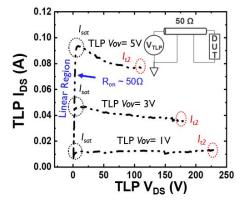

Fig. 3. 100 ns 50  $\Omega$  TLP I–V results for  $V_{\rm OV}$  of 1, 3, and 5 V. The  $V_{\rm OV}$  is equal to ( $V_{\rm GS}$ – $V_{\rm th}$ ). The  $V_{\rm GS}$  is the gate-to-source voltage, and the  $V_{\rm th}$  is the threshold voltage which is  $-5{\rm V}$  in the MIS-HEMTs. The source and substrate biases are grounded. In linear region, the ON-resistance ( $R_{\rm ON}$ ) is  $\sim$ 50  $\Omega$ . The current level in saturation region is determined by the channel driving capability. The  $I_{\rm IZ}$  are lower than the initial  $I_{\rm sat}$  [24], [28].

$L_G=1~\mu{\rm m},~L_{\rm GD}=1.75~\mu{\rm m},~L_{\rm GS}=1.5~\mu{\rm m},~{\rm and}~L_{\rm GFP}=0.5~\mu{\rm m}.$

# III. TLP VERSUS HBM

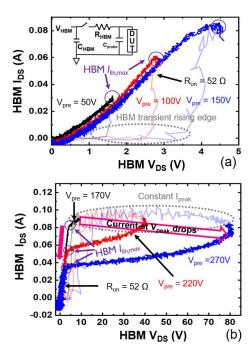

The inserted figure in Fig. 3 shows the simplified  $50-\Omega$ TLP setup. The TLP source is a square wave with 100 ns pulsewidth. The voltage and current values in the TLP I-Vare averagely calculated in each measured voltage and current waveform with the sampling window from 70% (70 ns) to 90% (90 ns) of the pulsewidth. Hence, the TLP I-V curves can be depicted in Fig. 3. On the other hand, the HBM source is principally made of a 100 pF capacitor and a 1.5 k $\Omega$  resistor, as shown in the inserted figure in Fig. 4(a). The HBM tester originally will only offer pass/fail levels for industrial qualification. However, in this article, the proposed transient HBM I-V [25] can provide additional information as compared to TLP I-V in GaN (MIS)HEMTs. The full transient HBM I-Vs are depicted from the voltage and current waveforms at a certain pre-charge voltage. Thus, the full time domain information is included in the transient HBM I-Vcurves.

The corresponding 50- $\Omega$  TLP I-V characteristics of the MIS-HEMTs with different overdrive voltages ( $V_{\rm OV}=1, 3, 5$  V) are shown in Fig. 3 [28]. Before current saturation, the  $R_{\rm ON}$  in the linear region of the transistor is similar for the different  $V_{\rm OV}$ . In the saturation region, the TLP saturation

Fig. 4. (a) HBM transient I-V curves with the  $V_{\rm pre}$  of 50, 100, and 150 V. The three HBM I-V curves all have a linear  $R_{\rm ON}$  of 52  $\Omega$  which is like TLP linear  $R_{\rm ON}$ . (b) HBM transient I-Vs with the  $V_{\rm pre}$  of 170, 220, and 270 V. The HBM transient rising edges induce the high  $V_{\rm DS}$  of  $\sim$ 40 and  $\sim$ 80 V in  $V_{\rm pre}$  of 220 and 270 V, respectively. Afterward, both  $V_{\rm DS}$  and  $I_{\rm DS}$  are progressively decreased in a saturation region. When  $V_{\rm DS} < V_{\rm OV}$  (5 V), the device operates again in the linear region. Moreover, the larger  $V_{\rm pre}$  has a lower  $I_{\rm lin,max}$  [28].

currents follow the individual DC channel driving capability at each  $V_{\rm OV}$ . The current collapse is observed as the drain voltage  $(V_{\rm DS})$  increases and the higher driving current facilitates the current collapse effect [29], [30]. This results in the  $I_{t2}$  level lower than the initial saturation current  $(I_{\rm sat})$ . However, these  $I_{t2}$  levels ( $\sim$ 10 to 80 mA) cannot match the measured >300 V HBM ESD robustness  $(V_{\rm HBM})$  based on the empirical correlation between HBM and TLP (Fig. 1). Consequently, the HBM transient I-V characteristics are used to understand the root cause of this mis-correlation.

The HBM transient I-Vs of the MIS-HEMTs are depicted at  $V_{\rm OV}$  of 5V in Fig. 4. In low HBM pre-charge voltage ( $V_{\rm pre}$  < 160 V), the maximum transient HBM linear current  $(I_{lin,max})$ is linearly increased with a fixed  $R_{\rm ON}$  of  $\sim$ 52  $\Omega$  [Fig. 4(a)], which is similar to the TLP  $R_{ON}$  in the linear region. However, as  $V_{\rm pre} > 160$  V, the  $V_{\rm DS}$  corresponding to HBM peak voltage  $(V_{\text{peak}})$  is significantly increased, as shown in Fig. 4(b). This results in a high-impedance discharge region. Eventually, when the  $V_{\rm DS}$  is back to the linear region condition, the discharge impedance can be aligned back to the linear  $R_{\rm ON}$  in Fig. 4(a). However, the corresponding  $I_{lin,max}$  is obviously reduced by increasing the HBM  $V_{pre}$ . The higher HBM  $V_{pre}$  induces higher  $V_{\text{peak}}$  and accompanies a more pronounced current drop from the  $I_{\text{peak}}$ . In addition, a large voltage drop from the higher HBM  $V_{\rm peak}$  to the low  $V_{\rm DS}$  in the linear region can cause further current drop during the saturation-to-linear transition. Fig. 5 shows the impact of different  $V_{OV}$  conditions on the peak current  $(I_{peak})$  and DUT impedance  $(Z_{DUT})$  extracted

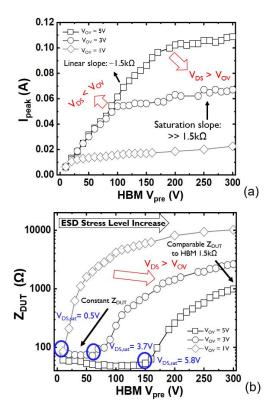

Fig. 5. HBM  $V_{\rm pre}$  versus (a) HBM transient  $I_{\rm peak}$  and (b) corresponding  $Z_{\rm DUT}$ .  $Z_{\rm DUT}$  are extracted from the HBM transient peak voltage ( $V_{\rm peak}$ ) and  $I_{\rm peak}$ . In the linear region ( $V_{\rm DS} < V_{\rm OV}$ ), the  $I_{\rm peak}$  is linearly increased while  $Z_{\rm DUT}$  maintains constant, whereas in the saturation region ( $V_{\rm DS} > V_{\rm OV}$ ),  $I_{\rm peak}$  is independent of  $V_{\rm pre}$  and  $Z_{\rm DUT}$  is consequently raised by increasing  $V_{\rm pre}$ . Different  $V_{\rm OV}$  determined the  $V_{\rm pre}$  deviation of the turning points to increase the  $Z_{\rm DUT}$  (blue circles) [28].

from the HBM transient waveforms. In Fig. 5(a), the  $I_{\rm peak}$  is linearly increased in the linear condition ( $V_{\rm DS} < V_{\rm OV}$ ). However, it saturates when  $V_{\rm DS} > V_{\rm OV}$ , where the  $Z_{\rm DUT}$  becomes critical and comparable with the HBM source resistor of 1.5 k $\Omega$ , as shown in Fig. 5(b). The measured  $V_{\rm DS,sat}$  values as the boundaries of linear and saturation are close to the corresponding  $V_{\rm OV}$  values. When the  $V_{\rm DS} > V_{\rm DS,sat}$ , the  $Z_{\rm DUT}$  starts to be modulated from low constant impedance ( $\sim 50~\Omega$ ) to high increasing impedance ( $> 900~\Omega$ ). These measured results imply that a different ESD HBM discharge mechanism exists in the GaN (MIS)HEMTs. The increase of the  $Z_{\rm DUT}$  by increasing  $V_{\rm peak}$  will be discussed in next section by TCAD and SPICE simulations.

### IV. HBM DISCHARGE MECHANISM

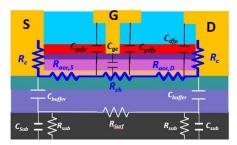

RC parasitic components exist in the RF GaN (MIS)HEMTs, as illustrated in Fig. 6 [31]. From the experiments in [28], the HBM discharge impedances in the linear region are determined by the resistance composed by the  $2R_C$ ,  $R_{acc,D}$ ,  $R_{ch}$ , and  $R_{acc,S}$  in the 2DEG. In order to investigate the reasons for increasing HBM discharge impedance in the saturation region, TCAD and SPICE simulations are used in the following paragraphs to understand the impact of the other RC components in Fig. 6.

Fig. 6. Parasitic RC model in GaN (MIS)HEMTs. The  $R_C$ ,  $R_{\mathrm{acc},D}$ ,  $R_{\mathrm{acc},S}$  and  $R_{\mathrm{ch}}$ , respectively, represent contact, drain-side access region, source-side access region, and channel resistance. The  $R_{\mathrm{suf}}$  and  $R_{\mathrm{sub}}$  are the interface resistance between the buffer and substrate and the resistance in the Si substrate.  $C_{\mathrm{buffer}}$  and  $C_{\mathrm{sub}}$  are the capacitance for buffer layer and substrate.  $C_{\mathrm{dfp}}$ ,  $C_{\mathrm{gc}}$ ,  $C_{\mathrm{gdfp}}$ ,  $C_{\mathrm{gsfp}}$ , represent drain-to-channel, gate-to-channel, gate field plate-to-channel (drain-side), and gate field plate-to-channel (source-side) capacitance, respectively, [28], [31].

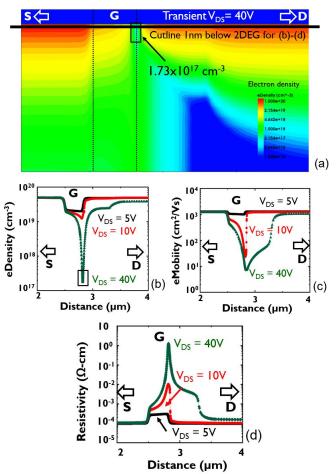

Fig. 7. (a) TCAD simulation results of the electron density ( $N_e$ ) in cross-sectional view at transient  $V_{\rm DS}$  of 40 V. The horizontal line in the cross-sectional view is cut at 1 nm below the 2DEG surface to observe the distribution from source to drain. The distribution of (b)  $N_e$ , (c) electron mobility ( $\mu_n$ ), and (d) resistivity in the horizontal cutline view with the transient  $V_{\rm DS}$  of 5, 10, and 40 V. Both the  $N_e$  and  $\mu_n$  significantly dropped at the gate corner to the drain side when the  $V_{\rm DS}$  is increased from 5 to 40 V, resulting in the resistivity significantly increased [28].

TCAD simulations by Synopsys Sentaurus Device are deployed with transient source at the drain side and with the gate and the source of the GaN (MIS)HEMT grounded. The resistivity of the 2DEG channel can be calculated by

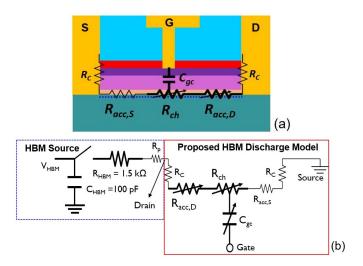

Fig. 8. (a) Calibrated HBM transient RC discharge model in GaN (MIS)HEMTs. (b) Schematic of HBM source and proposed HBM discharge model. The HBM source which has been simplified by removing some parasitic components in [28] includes the parasitic resistance  $(R_p)$  of the probe needles.

the equation of  $(q \times \mu_n \times N_e)^{-1}$ , where q is the electron charge,  $\mu_n$  is the electron mobility, and  $N_e$  is the electron density. Fig. 7(b) shows that electron density  $(N_e)$  significantly reduced from  $10^{20}$  cm<sup>-3</sup> to  $10^{17}$  cm<sup>-3</sup> by increasing  $V_{DS}$  from 5 V (linear region) to 40 V (saturation region) due to the channel pinch-off. The depletion area is located at the gate corner of the drain side and the gate-to-drain access region in the vicinity of the gate. The cutline depth in Fig. 7(b)–(d) is the 1 nm below the interface of the 2DEG channel to observe the parameters in the equation varied by the  $V_{DS}$  increase [28]. Not only  $N_e$  is significantly reduced [Fig. 7(b)], but also the  $\mu_n$  drops  $\sim 100 \times$  from the  $V_{\rm DS}$  of 5 to 40 V [Fig. 7(c)]. With the increasing transient  $V_{DS}$ , the overall resistance mainly corresponding to the  $R_{ch}$  at the gate corner of the drain side can be modulated more than  $\sim 10 \text{ k}\Omega \cdot \text{cm}$  [Fig. 7(d)]. Besides, the piece of  $R_{acc,D}$  near the gate corner is also modulated by the high transient  $V_{DS}$ . From the simulation results, the impedance increase in the saturation region comes from the  $R_{\rm ch}$  and  $R_{{\rm acc},D}$ .

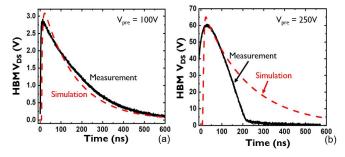

The impact of the parasitic capacitance on HBM  $V_{\text{peak}}$  for the buffer thickness variation and the chuck bias conditions have been presented [28]. It is proved that the  $C_{\text{buffer}}$  and  $C_{\text{sub}}$ have no influence on  $V_{\text{peak}}$ . From the calculated individual parasitic capacitors indicates that the  $C_{\rm gc}$  is dominant among the other capacitors [28]. Thus, compared to the other capacitors,  $C_{\rm gc}$  can be seen as a dominant capacitor in the HBM transient discharge model [Fig. 8(a)]. The schematic of the proposed HBM transient discharge model in the GaN (MIS)HEMTs with the simplified equivalent circuit of HBM ESD source is depicted in Fig. 8(b). The SPICE simulations by Keysight ADS are constructed to verify the impacts of  $R_{ch}$ ,  $R_{acc,D}$ , and  $C_{\rm gc}$  on HBM discharge mechanism. All the RC values are extracted from the measurement results. In a linear region with the  $V_{\rm pre}$  of 100 V, the simulated voltage waveform is perfectly matched to the measurement [Fig. 9(a)]. From the RC time

Fig. 9. HBM voltage waveforms of SPICE simulation and HBM measurement in (a)  $V_{\rm pre}=100$  V, and (b)  $V_{\rm pre}=250$  V. The fixed  $R_{\rm DS}$  values in simulation can match to the measurement waveform in  $V_{\rm pre}=100$  V (linear region), whereas it cannot match to the measurement in  $V_{\rm pre}=250$  V (saturation region) due to the dynamic  $R_{\rm ch}$  and  $R_{\rm acc,D}$  during the falling edge of discharge waveform [28].

constant  $(\tau_{\rm rc})$ , the R is mainly related to the sum of  $R_{\rm HBM}$  in the HBM source and the total resistance in the model, and the C is only dominated by the  $C_{\rm HBM}$  of 100 pF.  $C_{\rm gc}$  is too small to impact the HBM waveforms. In Fig. 9(b), the simulated  $V_{\rm peak}$  in the  $V_{\rm pre}$  of 250 V is consistent with the measured  $V_{\rm peak}$ . However, the full simulated discharge waveform cannot match the measured result.

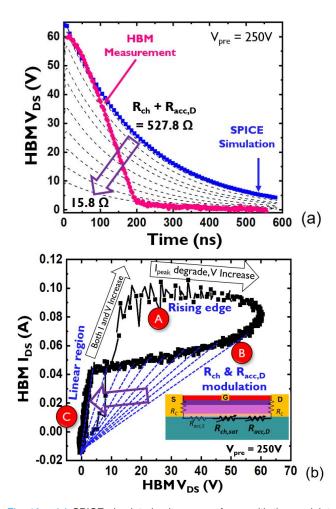

This mismatch is attributed to a fixed simulated  $R_{DS}$ . In fact, the TCAD results have indicated the  $R_{ch}$  and  $R_{acc,D}$  can be significantly modulated by high  $V_{\rm DS}$ . This modulated  $R_{\rm ch}$ and  $R_{\text{acc},D}$  can directly bring the impact on  $R_{\text{DS}}$  (2 $R_{\text{C}}$  +  $R_{\text{acc},S} + R_{\text{acc},D} + R_{\text{ch}}$ ). With the modulated  $R_{\text{ch}}$  and  $R_{\text{acc},D}$ from 527.8 to 15.8  $\Omega$  depicted in Fig. 10(a) (dash lines), the measured voltage waveform will follow these modulation dash lines. Eventually, the waveform follows the linear region with the constant impedance. Fig. 10(b) demonstrates the discharge mechanism during the full HBM transient I-V. At the beginning of the HBM rising edge, the high  $V_{\text{pre}}$  of 250 V suddenly increases  $V_{DS}$  and  $I_{DS}$ . As the  $V_{DS}$  increased (phase A), the  $I_{\rm peak}$  can be obtained at the  $V_{\rm DS}$  of  $\sim 36$  V. Afterward, the  $I_{\rm DS}$ progressively decreases until the  $V_{DS} = V_{peak}$ . After the  $V_{peak}$ (phase B), the  $R_{ch}$  and  $R_{acc,D}$  are modulated from the order of 527.8 to 15.8  $\Omega$  as the  $V_{\rm DS}$  decreased in the saturation discharge region illustrated in Fig. 10(a). The  $R_{ch}$  and  $R_{acc,D}$ modulation will be ended until the  $V_{DS}$  back to the linear discharge region (phase C).

# V. DISCUSSION

# A. Physical Mechanism Under HBM Transient Rising Edge

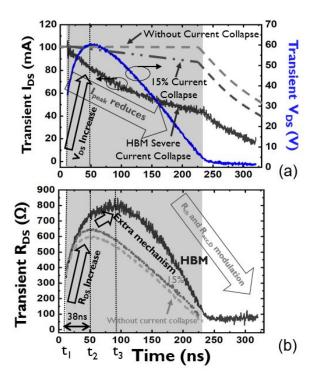

In the HBM model, the HBM  $V_{\rm pre}$  discharges the DUT through the 1.5 k $\Omega$  resistor. In a low-impedance DUT  $(R_{\rm DUT} \ll 1.5 \ {\rm k}\Omega)$ , the  $I_{\rm peak}$  will be mainly determined by the 1.5 k $\Omega$  resistor and the  $V_{\rm peak}$  is from the IR drop of the  $I_{\rm peak}$  and  $R_{\rm DUT}$ . In the GaN (MIS)HEMTs, however, the high impedance in the saturation region limits the  $I_{\rm peak}$ , which matches the maximum 2DEG driving capability  $(I_{\rm max})$ . The limited  $I_{\rm peak}$  discharging through the 1.5 k $\Omega$  generates a lower voltage drop, which consequently increases the voltage potential at the drain terminal of the GaN (MIS)HEMTs. This can cause the obvious rising time difference ( $\sim$ 40 ns)

Fig. 10. (a) SPICE simulated voltage waveforms with the modulated  $(R_{\mathrm{acc},D} + R_{\mathrm{ch}})$  from 527.8 to 15.8  $\Omega$  under the pre-charge voltage  $(V_{\mathrm{pre}})$  of 250 V are shown as the dash lines. The measured HBM voltage waveform can follow the simulated waveforms with different  $(R_{\mathrm{acc},D} + R_{\mathrm{ch}})$  values. This demonstrates that the  $(R_{\mathrm{acc},D} + R_{\mathrm{ch}})$  are dynamically modulated during the discharge period. (b) Corresponding measured HBM transient I–V characteristics are defined with three different discharge phases. During the rising edge (phase A), the high  $V_{\mathrm{pre}}$  of 250 V causes the abruptly raising  $V_{\mathrm{DS}}$  and  $I_{\mathrm{DS}}$ . After the  $I_{\mathrm{peak}}$ , the  $V_{\mathrm{DS}}$  is still raising to the  $V_{\mathrm{peak}}$  while the  $I_{\mathrm{DS}}$  slightly degrades. Phase A ends when the  $V_{\mathrm{DS}}$  reaches to  $V_{\mathrm{peak}}$ . After the  $V_{\mathrm{peak}}$ , due to the  $(R_{\mathrm{acc},D} + R_{\mathrm{ch}})$  dynamic modulation, the  $V_{\mathrm{DS}}$  and  $I_{\mathrm{DS}}$  are gradually decreased following the high impedance change in phase B. When  $V_{\mathrm{DS}}$  drops <5 V (phase C), the  $(R_{\mathrm{acc},D} + R_{\mathrm{ch}})$  modulation is ended and the resistance is back to the constant 52  $\Omega$  in the linear region (phase C) [28].

between HBM transient voltage and current waveforms, as shown in Fig. 11(a). The  $I_{\rm DS}$  and  $V_{\rm DS}$  will be adjusted by following Kirchhoff's voltage law (KVL) during the  $t_1$  and the  $t_2$  in Fig. 11. However, a significant current collapse which is induced by an extra mechanism is observed in the HBM transient waveforms. In the ideal case without any current collapse, the  $I_{\rm peak}$  follows the constant saturated current  $I_{\rm DS,sat}$ , which is equaled to the  $I_{\rm max}$ . In reality, the current collapse of the saturated  $I_{\rm DS}$  has been observed in the TLP I-Vs with <100 ns stress duration. Fig. 3 shows the 15% of current collapse at the  $V_{\rm OV}$  of 5 V. Nonetheless, the current collapse in the measured HBM current waveform is much pronounced than the 15% current collapse. It implies the extra mechanism

Fig. 11. (a) Measured HBM voltage and current waveforms at  $V_{\rm pre}=250~{\rm V}$  with two illustrated current waveforms without current collapse and 15% current collapse. (b) Corresponding transient  $R_{\rm DS}$ . At the rising edge, the  $I_{\rm peak}$  ( $t_1$ ) occurs earlier than  $V_{\rm peak}$  ( $t_2$ ). With the severe current collapse, the peak  $R_{\rm DS}$  is after the  $V_{\rm peak}$ , as compared to the peak  $R_{\rm DS}$  which is aligned to the  $V_{\rm peak}$  without the severe current collapse. After the  $V_{\rm peak}$ , the device starts to discharge with the transient resistance modulation and extra mechanism until back to the constant  $R_{\rm DS}$ .

of the current collapse under the HBM stresses. The corresponding transient  $R_{\rm DS}$ , as shown in Fig. 11(b), also indicates that the time of peak  $R_{\rm DS}$  aligns to the  $V_{\rm peak}$  without the severe current collapse. However, with the severe current collapse in the measured HBM current waveform, the peak  $R_{\rm DS}$  will be shifted from the  $V_{\rm peak}$  at  $t_2$  (50 ns) to  $t_3$  (95 ns). The transient resistance modulation is not only determined by the  $I_{\rm max}$  but also impacted by the severe current collapse induced by the extra mechanism. This extra mechanism might be attributed to additional nano-seconds transient trapping effects from [29].

# B. GaN (MIS)HEMTs Versus CMOS LV Transistors

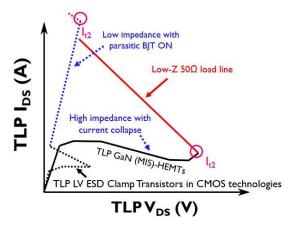

Different from the GaN (MIS)-HEMTs, an ESD clamp transistor in LV CMOS technology has a parasitic BJT which can provide a low-impedance discharge current path while it triggered. Its impedance is typically lower than 50  $\Omega$  of the TLP tester. Consequently, its  $I_{t2}$  can well correlate to the  $V_{\rm HBM}$  with a factor of  $\sim 1.5$  k $\Omega$ . However, the GaN (MIS)-HEMT has an impedance much higher than 50  $\Omega$  (close to 100-1 k $\Omega$ ) after the current saturation. This high impedance induces the mis-correlation between TLP  $I_{t2}$  and  $V_{\rm HBM}$  (Fig. 12). In order to roughly estimate the HBM robustness from TLP  $I_{t2}$ , the impedance of GaN (MIS)HEMTs should be considered in a revised correlation of  $V_{\rm HBM} = I_{t2} \times (R_{\rm HBM} + R_{\rm DS})$ . However, the severe current collapse observed in the HBM current

Fig. 12. Illustrated TLP I–V characteristics of the ESD clamp transistors in LV CMOS technologies and GaN (MIS)HEMTs. As compared to LV CMOS device, the GaN transistor does not have parasitic BJT providing low-impedance current path before it failed. Instead, the GaN TLP current is saturated with much higher impedance than the 50  $\Omega$  TLP tester. The high impedance can induce the mis-correlation between TLP I<sub>IZ</sub> and HBM ESD robustness (V<sub>HBM</sub>) [28].

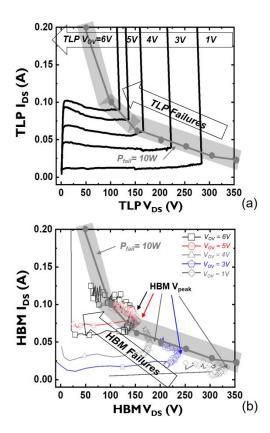

Fig. 13. Measured (a) TLP I–V curves and (b) HBM transient I–V curves with different  $V_{OV}$  after the device failures. The constant failure power of 10 W is illustrated. Both on-state TLP and HBM follow the power failure mechanisms [22], [24].

waveform can induce an additional  $R_{\rm DS}$  deviation from the revised correlation.

# C. Failure Mechanisms in TLP and HBM

The benefits of the HBM transient I-Vs which can provide more information than the TLP I-V have been revealed

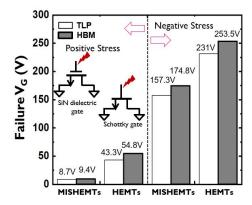

Fig. 14. GaN (MIS)HEMT gate failures in the TLP and HBM tests. Both TLP and HBM stress configuration in the gate immunity tests are zapping gate terminal with drain—source, and substrate grounded. The TLP and HBM failure voltages are consistent in both positive and negative stresses [24].

in [28]. However, a completed failure mechanism in HBM ESD stress has not yet been disclosed. Fig. 13(a) indicates the ON-state TLP failures of the GaN (MIS)HEMTs follow the constant power curve of 10 W. The deviation can be observed in the low  $V_{OV}$  bias conditions ( $V_{OV} = 1-3$  V). This ON-state failure mechanism has been proposed in [22]. Furthermore, Fig. 13(b) shows the ON-state HBM failure mechanisms, which approximately follows the same constant power curve in the TLP results [Fig. 13(a)]. Different from the TLP results, the deviation of the ON-state HBM failures at the  $V_{\text{peak}}$  from the constant power curve can be seen in each  $V_{\rm OV}$ . The root cause may be related to the severe current collapse and different sampling windows of the captured I-V characteristics between TLP and HBM. On the other hand, in [22] and [24], OFF-state TLP failure mechanisms are determined by the constant voltage (electric-field), which is intrinsically attributed to the gate immunity of the devices. Fig. 14 presents the gate immunity in the MIS-HEMTs under the TLP and the HBM tests. The TLP gate immunity tests have been discussed in [24]. The HEMTs which have higher TLP failure levels in terms of positive and negative stresses are also evaluated. The corresponding HBM gate immunity tests are included in Fig. 14. Compared with the TLP failure levels [24], the slightly higher HBM failure voltages directly captured at the gate terminal could be attributed to the different sampling windows in the TLP and HBM. Overall, the OFFstate failure mechanisms of the GaN-on-Si MIS-HEMTs and HEMTs are consistent in the TLP and HBM.

# VI. CONCLUSION

In this work, the mis-correlation between TLP  $I_{t2}$  and  $V_{\rm HBM}$  has been investigated in detail. The new proposed HBM discharge model with the dynamic resistance modulation is revealed and successfully explains the HBM transient discharge mechanism. This modulation induces the total discharge impedance variation from  $\sim 560$  to  $\sim 52~\Omega$  under the  $V_{\rm pre}$  of 250 V. By the TCAD and SPICE simulations, the root cause of the resistance modulation is attributed to the influence of the  $V_{\rm DS}$  on  $\mu_n$  and  $N_e$  in the 2DEG channel ( $R_{\rm ch}$ ) and

the drain access region ( $R_{\mathrm{acc},D}$ ). The severe current collapse induced the extra mechanism has been observed under the HBM transient current waveform. This caused more pronounced resistance modulation under the HBM ESD stresses. The revised correlation between the TLP  $I_{t2}$  and HBM robustness ( $V_{\mathrm{HBM}}$ ) has been proposed. However, the extra parasitic components in HBM source, the severe current collapse in the HBM current waveforms, and different sampling windows between TLP and HBM can bring the influence on the revised correlation. Finally, the TLP and HBM failure mechanisms have been completely compared in the ON-state and OFF-state GaN (MIS)HEMTs. In general, the ON-state and OFF-state failures in the TLP and HBM still follow the constant power and electric field mechanisms, respectively.

# REFERENCES

- [1] R. Giofre, A. D. Gaudio, and E. Limiti, "A 28 GHz MMIC Doherty power amplifier in GaN on Si technology for 5G applications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2019, pp. 611–613, doi: 10.1109/MWSYM.2019.8700757.

- [2] H. W. Then et al., "Gallium nitride and silicon transistors on 300 mm silicon wafers enabled by 3-D monolithic heterogeneous integration," *IEEE Trans. Electron Devices*, vol. 67, no. 12, pp. 5306–5314, Dec. 2020, doi: 10.1109/TED.2020.3034076.

- [3] U. K. Mishra, P. Parikh, and Y.-F. Wu, "AlGaN/GaN HEMTs—An overview of device operation and applications," *Proc. IEEE*, vol. 90, no. 6, pp. 1022–1031, Jun. 2002, doi: 10.1109/JPROC.2002.1021567.

- [4] A. Aminbeidokhti, S. Dimitrijev, J. Han, X. Chen, and X. Xu, "The power law of phonon-limited electron mobility in the 2-D electron gas of AlGaN/GaN heterostructure," *IEEE Trans. Electron Devices*, vol. 63, no. 5, pp. 2214–2218, May 2016, doi: 10.1109/TED.2016.2544920.

- [5] L. Ardaravičius, J. Liberis, O. Kiprijanovič, A. Matulionis, M. Wu, and H. Morkoç, "Hot-electron drift velocity and hot-phonon decay in AlInN/AlN/GaN," *Phys. Status Solidi (RRL)-Rapid Res. Lett.*, vol. 5, no. 2, pp. 65–67, Feb. 2011, doi: 10.1002/PSSR.201004502.

- [6] J. Khurgin, Y. J. Ding, and D. Jena, "Hot phonon effect on electron velocity saturation in GaN: A second look," Appl. Phys. Lett., vol. 91, no. 25, Dec. 2007, Art. no. 252104, doi: 10.1063/1.2824872.

- [7] N. Collaert et al., "Semiconductor technologies for next generation mobile communications," in Proc. 14th IEEE Int. Conf. Solid-State Integr. Circuit Technol. (ICSICT), Oct. 2018, pp. 1–4, doi: 10.1109/ICSICT.2018.8565822.

- [8] S. Turuvekere, N. Karumuri, A. A. Rahman, A. Bhattacharya, A. Dasgupta, and N. DasGupta, "Gate leakage mechanisms in AlGaN/GaN and AlInN/GaN HEMTs: Comparison and modeling," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3157–3165, Oct. 2013, doi: 10.1109/TED.2013.2272700.

- [9] H. W. Then et al., "Experimental observation and physics of 'negative' capacitance and steeper than 40 mV/decade subthreshold swing in Al<sub>0.83</sub>In<sub>0.17</sub>N/AIN/GaN MOS-HEMT on SiC substrate," in *IEDM Tech. Dig.*, Dec. 2013, pp. 28.3.1–28.3.4, doi: 10.1109/IEDM.2013.6724709.

[10] M. Van Hove et al., "CMOS process-compatible high-power low-leakage

- [10] M. Van Hove et al., "CMOS process-compatible high-power low-leakage AlGaN/GaN MISHEMT on silicon," *IEEE Electron Device Lett.*, vol. 33, no. 5, pp. 667–669, May 2012, doi: 10.1109/LED.2012.2188016.

- [11] N. Zagni et al., "Trap dynamics model explaining the R<sub>ON</sub> stress/recovery behavior in carbon-doped power AlGaN/GaN MOS-HEMTs," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2020, pp. 1–5, doi: 10.1109/IRPS45951.2020.9128816.

- [12] S. D. Gupta, V. Joshi, R. R. Chaudhuri, A. K. Singh, S. Guha, and M. Shrivastava, "On the root cause of dynamic ON resistance behavior in AlGaN/GaN HEMTs," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2020, pp. 1–4, doi: 10.1109/IRPS45951.2020.9128226.

- [13] V. Putcha et al., "On the impact of buffer and GaN-channel thickness on current dispersion for GaN-on-Si RF/mmWave devices," in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), Mar. 2021, pp. 1–8, doi: 10.1109/IRPS46558.2021.9405139.

- [14] T.-L. Wu et al., "Time dependent dielectric breakdown (TDDB) evaluation of PE-ALD SiN gate dielectrics on AlGaN/GaN recessed gate D-mode MIS-HEMTs and E-mode MIS-FETs," in Proc. IEEE Int. Rel. Phys. Symp., Apr. 2015, pp. 6C.4.1–6C.4.6, doi: 10.1109/IRPS.2015.7112769.

- [15] Y. Qi et al., "Evaluation of LPCVD SiNx gate dielectric reliability by TDDB measurement in Si-substrate-based AlGaN/GaN MIS-HEMT," *IEEE Trans. Electron Devices*, vol. 65, no. 5, pp. 1759–1764, May 2018, doi: 10.1109/TED.2018.2813985.

- [16] T.-L. Wu et al., "Correlation of interface states/border traps and threshold voltage shift on AlGaN/GaN metal-insulator-semiconductor high-electron-mobility transistors," Appl. Phys. Lett., vol. 107, no. 9, Aug. 2015, Art. no. 093507, doi: 10.1063/1.4930076.

- [17] D. Bisi et al., "Observation of hot electron and impact ionization in N-polar GaN MIS-HEMTs," *IEEE Electron Device Lett.*, vol. 39, no. 7, pp. 1007–1010, Jul. 2018, doi: 10.1109/LED.2018.2835517.

- [18] V. Putcha et al., "Exploring the DC reliability metrics for scaled GaN-on-Si devices targeted for RF/5G applications," in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), Apr. 2020, pp. 1–8, doi: 10.1109/IRPS45951.2020.9129251.

- [19] Standard Test Method for Electrostatic Discharge (ESD) Sensitivity Testing: Human Body Model (HBM)-Component Level, ESD Association Standard ANSI/ESDA/JEDEC JS-001-2017, 2017.

- [20] B. Shankar, S. D. Gupta, A. Soni, S. Raghavan, and M. Shrivastava, "ESD behavior of AlGaN/GaN Schottky diodes," *IEEE Trans. Device Mater. Rel.*, vol. 19, no. 2, pp. 437–444, Jun. 2019, doi: 10.1109/TDMR.2019.2916846.

- [21] A. Tazzoli, F. Danesin, E. Zanoni, and G. Meneghesso, "ESD robustness of AlGaN/GaN HEMT devices," in *Proc. 29th Electr. Overstress/Electrostatic Discharge Symp. (EOS/ESD)*, Sep. 2007, pp. 4A.4-1–4A.4-9, doi: 10.1109/EOSESD.2007.4401762.

- [22] I. Rossetto et al., "Demonstration of field- and power-dependent ESD failure in AlGaN/GaN RF HEMTs," IEEE Trans. Electron Devices, vol. 62, no. 9, pp. 2830–2836, Sep. 2015, doi: 10.1109/TED.2015.2463713.

- [23] B. Shankar, S. Raghavan, and M. Shrivastava, "ESD reliability of AlGaN/GaN HEMT technology," *IEEE Trans. Electron Devices*, vol. 66, no. 9, pp. 3756–3763, Sep. 2019, doi: 10.1109/TED.2019.2926781.

- [24] W.-M. Wu et al., "ESD failures of GaN-on-Si D-mode AlGaN/GaN MIS-HEMT and HEMT devices for 5G telecommunications," in Proc. 43rd Annu. EOS/ESD Symp. (EOS/ESD), Sep. 2021, pp. 1–7, doi: 10.23919/EOS/ESD52038.2021.9574716.

- [25] M. Scholz et al., "ESD on-wafer characterization: Is TLP still the right measurement tool?" *IEEE Trans. Instrum. Meas.*, vol. 58, no. 10, pp. 3418–3426, Oct. 2009, doi: 10.1109/TIM.2009.2017657.

- [26] S.-H. Chen et al., "HBM ESD robustness of GaN-on-Si Schottky diodes," *IEEE Trans. Device Mater. Rel.*, vol. 12, no. 4, pp. 589–598, Dec. 2012, doi: 10.1109/TDMR.2012.2217746.

- [27] U. Peralagu et al., "CMOS-compatible GaN-based devices on 200 mm-Si for RF applications: Integration and performance," in IEDM Tech. Dig., Dec. 2019, pp. 17.2.1–17.2.4, doi: 10.1109/IEDM19573.2019.8993582.

- [28] W.-M. Wu et al., "ESD HBM discharge model in RF GaN-on-Si (MIS)HEMTs," in IEDM Tech. Dig., Dec. 2021, pp. 39.5.1–39.5.4.

- [29] M. Meneghini et al., "Trapping in GaN-based metal-insulator-semiconductor transistors: Role of high drain bias and hot electrons," Appl. Phys. Lett., vol. 104, no. 14, Apr. 2014, Art. no. 143505, doi: 10.1063/1.4869680.

- [30] X. Chen, S. Boumaiza, and L. Wei, "Self-heating and equivalent channel temperature in short gate length GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 66, no. 9, pp. 3748–3755, Sep. 2019, doi: 10.1109/TED.2019.2926742.

- [31] S. Yadav et al., "Substrate RF losses and non-linearities in GaN-on-Si HEMT technology," in IEDM Tech. Dig., Dec. 2020, pp. 8.2.1–8.2.4, doi: 10.1109/IEDM13553.2020.9371893.