# BEOL N2: M2 through SAxP Process from MP21 to MP26: 193i SAQP vs EUV SADP

Yannick Hermans<sup>\*</sup>, Chen Wu, Nunzio Buccheri, Filip Schleicher, Janko Versluijs, Daniel Montero, Bappaditya Dey, Patrick Wong, Paulina Rincon-Delgadillo, Seongho Park, Zsolt Tokei, Philippe Leray, Sandip Halder imec, Kapeldreef 75, Heverlee 3001, Belgium

#### **ABSTRACT**

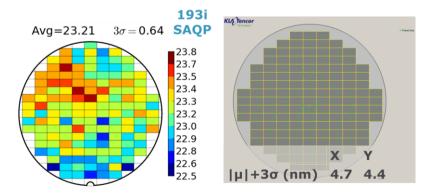

193i SAQP has allowed industry for continued BEOL metal pitch scaling, but as metal pitches become even tighter EUV SADP becomes an interesting alternative. In this context we have explored within our dual damascene 3ML test vehicles how the EUV SADP process compares to 193i SAQP for printing MP21 M2 lines. Our first EUV SADP results already show a better wafer CDU compared to our POR 193i SAQP process.

Keywords: multiple patterning, EUV lithography, back end of line, metal pitch 21, line edge roughness, CD uniformity

#### 1. INTRODUCTION

Multiple patterning techniques have allowed industry to pattern beyond the resolution of 193i lithography. Various multiple patterning techniques have been explored such as litho-etch-litho-etch (LELE)<sup>1</sup> or directed self-assembly (DSA)<sup>2</sup> but one of the most acknowledged techniques is self-aligned multiple patterning (SAxP).<sup>3</sup> Nowadays, 193i self-aligned quadruple patterning (SAQP) is the established process for patterning fins<sup>4</sup> and interconnect metal lines.<sup>5</sup> In recent years, however, extreme ultraviolet (EUV) lithography has matured enough to become a contender for 193i multiple patterning. Nevertheless, for the N2 technology node, EUV lithography would need to adopt the multiple patterning approach as well if it wants to keep up with 193i SAQP for the tightest pitches.<sup>6</sup>

Within the back end of line (BEOL), simplification of the electrical wiring is key to enable further die area shrinkage. This, in turn, allows for a higher yield per wafer and, thus, a lower die cost. Die area scaling can be achieved using so-called scaling boosters. Some of the most actively explored scaling boosters include the fully self-aligned via (FSAV),<sup>7</sup> the supervia (SV)<sup>8</sup> and vertical-horizontal-vertical (VHV) routing.<sup>9</sup> Moreover, traditional Cu dual damascene (DD) metal filling is also challenged through the exploration of new metallization techniques such as the Ru dual damascene or Ru semi-damascene process.<sup>11</sup> Meanwhile, traditional metal pitch scaling continues as well, which is where multiple patterning comes in. Herein, EUV self-aligned double patterning (SADP) challenges the established 193i SAQP process for reaching metal pitch 21 (MP21).

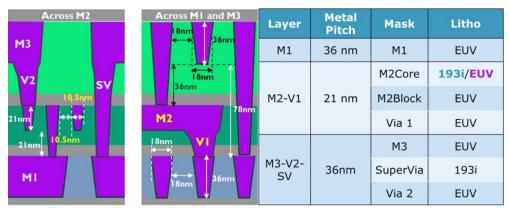

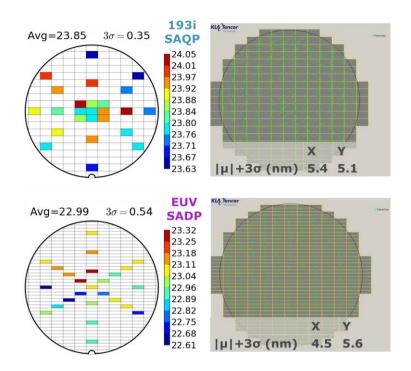

In this work, we have explored within our BEOL three-metal-layer (3ML) dual damascene test vehicles (Figure 1) how EUV SADP compares to 193i SAQP for patterning metal 2 (M2) lines up to MP21. Our first results on EUV SADP patterning already demonstrate a better wafer critical dimension uniformity (CDU) between and within metal trench populations compared to our process-of-reference (POR) 193i SAQP process. Moreover, the electrical resistance of the EUV SADP metal lines after Ru DD metal filling comes close to our 193i SAQP process.

<sup>\*</sup> yannick.hermans@imec.be

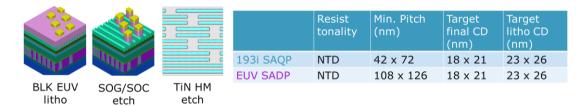

Figure 1: 3ML dual damascene test vehicle schematic, dimensions, and lithography steps.

## 2. RESULTS

# 2.1 M2Core: 193i SAQP vs EUV SADP: target 21 nm MP

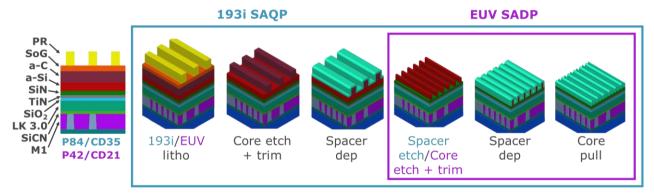

The first step to reach the MP21 target is the processing of the M2Core module. Figure 2 shows schematically which steps are followed during the M2Core module following the 193i SAQP and EUV SADP process. In 193i SAQP a line/space pattern is printed using 193i lithography with a target CD of 35 nm and a target pitch of 84 nm. The core lines are then etched and trimmed into the amorphous carbon layer, after which the first oxide spacer is grown. After core pull, the spacer lines are transferred into amorphous silicon (a-Si), followed by the growth of a SiO<sub>x</sub> spacer. Finally, the a-Si core will be removed, leaving behind a set of spacer lines. In this way three types of trenches are formed: core (from litho step), gap (from litho step) and spacer (from spacer 1 deposition). In EUV SADP, the EUV lithography step targets a 21 nm CD and a 42 nm pitch. Then, the core is etched and trimmed directly into a-Si. This step is followed by spacer deposition and concluded with the core pull. After EUV SADP only two trench types are formed: core and gap.

Figure 2: M2Core patterning stack and steps for the 193i SAQP and EUV SADP process.

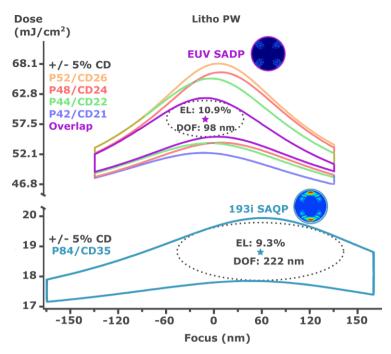

Figure 3 shows the process windows (+/- 5%) for the 193i and EUV lithography steps. For EUV an overlapping process window is created from the P42/CD21 target up to P52/CD26, while for 193i SAQP just the P84/CD35 (+-5% CD) target is used. Whether EUV or 193i is superior cannot be concluded from these process windows considering that different sources and resists (chemically amplified resist (CAR) for 193i and metal oxide resist (MOR) for EUV) have been used. Nevertheless, both lithography processes offer a workable process window with the EUV lithography process having a somewhat higher exposure latitude (EL) and lower depth of focus (DOF) compared to the 193i lithography process.

Figure 3: M2Core lithography process window for the 193i SAQP (using CAR resist) and EUV SADP (using MOR resist) process.

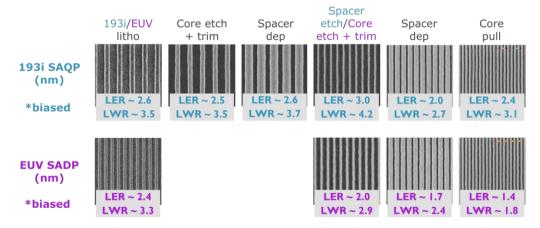

The Critical Dimension Scanning Electron Microscopy (CDSEM) images in **Error! Reference source not found.** show a considerably lower biased line edge roughness (LER) and line width roughness (LWR) for the EUV SADP process from the "193i spacer etch/EUV core etch + trim" step until the "core pull" step. This is a positive trend, but the actual values should be taken with a grain of salt, because the metrology component remains in biased LER and LWR values. Most measurements have been performed on the same tools under the same conditions, though.

Figure 4: M2Core CDSEM images after each step in the 193i SAQP and EUV SADP process. The biased LER and LWR values shown here correspond to the core/hole populations. The CDSEM images correspond to the pitch 21 target.

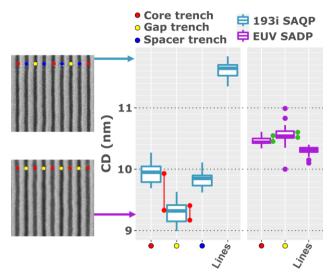

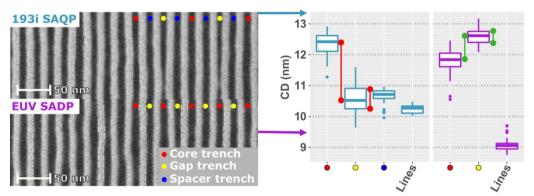

The average CD boxplots across wafer in Figure 5 demonstrate a better CDU between and within trench populations for the EUV SADP process compared to the 193i SAQP process. This is a highly positive result for EUV SADP, since having a low CD variability between trenches is crucial for maintaining uniform electrical wiring.

Figure 5: Average CD boxplots across wafer for the different trench populations and lines after core pull for the 193i SAQP and EUV SADP process. The CDSEM images and boxplots correspond to the pitch 21 target.

#### 2.2 M2Block

After the M2Core module comes the M2Block module. The M2Block module has the purpose to cut away spacer line ends as well as cutting the lines at certain places. Figure 6 shows the patterning steps as well as the target dimensions for the block pattern. After the lithography step, SOG and SOC will be etched, followed by a transfer into TiN.

Figure 6: M2Block patterning steps and target dimensions for the 193i SAQP and EUV SADP process.

For both the 193i SAQP and EUV SADP process flow good wafer CDU as well as good M2Block-to-M2Core overlay has been achieved as can be seen in Figure 7.

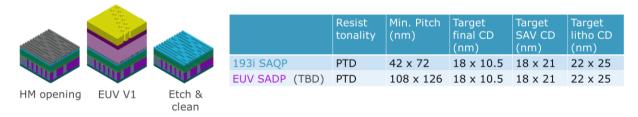

### 2.3 Via 1 + low k etch

The M2Block module is then normally followed by the Via 1 module. In the Via 1 module, the vias that connect M1 to M2 are printed. Then, they are transferred together with the M2 lines into the low k dielectric (Figure 8). For the EUV SADP process flow the complete M1M2V1 short loop is still under development. The Via 1 printing has, thus, been skipped for EUV SADP. Instead, the M2Core + M2Block TiN hard mask pattern is immediately etched into low k. Meanwhile, for 193i SAQP a good Via 1 wafer CDU as well as a good Via 1-to-M2Core has been obtained (Figure 9).

The CDSEM images after the low k etch (Figure 10) show that both 193i SAQP as well as EUV SADP suffer from line wiggling as well as pitch walking. Both phenomena are detrimental for uniform electrical performance and should be reduced as much as possible. The boxplots which show the average trench/line CD across the wafer still show that the CDU between and within trench populations is better for EUV SADP compared to 193i SAQP. The CDU has become worse though for both process flows compared to the "Core pull step" in the M2Core module. Additionally, the CD for the MP21 EUV SADP trenches is a bit above the aimed 11 nm target. In the next iteration, this can be solved though by depositing a slightly thicker spacer.

Figure 7: wafer CDU and M2Block-to-M2Core overlay wafer map after the M2Block lithography step for the 193i SAQP and EUV SADP process.

Figure 8: Via 1 patterning steps and target dimensions for the 193i SAQP and EUV SADP process.

Figure 9: wafer CDU and Via 1-to-M2Core overlay wafer map after the Via 1 lithography step for the 193i SAQP process.

Figure 10: CDSEM images and average CD boxplots across wafer for the different trench populations and lines after low k etch for the 193i SAQP and EUV SADP process. The CDSEM images and boxplots correspond to the MP21 target.

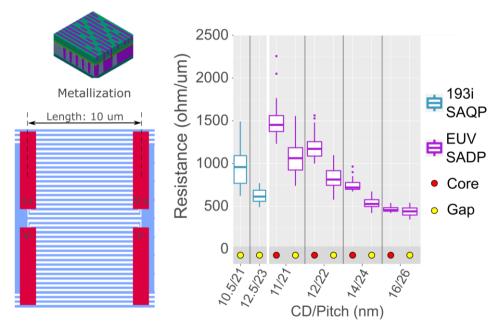

#### 2.4 Metallization and electrical testing

After Via 1 patterning and etching into low k, a dual damascene process is used to fill the M2 trenches and vias with Ru metal. As the Via 1 module has not yet been developed for the EUV SADP process, it's factually following a single damascene process at this point. Consequently, this limits the electrical testing to M2 metal line resistance measurements as depicted in Figure 11. Despite the EUV SADP MP21 gap trenches having a higher CD they exhibit a higher resistance compared to the 193i SAQP MP21 gap trenches. The differences are rather small though and might be chemical mechanical polishing (CMP) related or due to the observed pitch walking. For the EUV SADP process the core metal lines also have a higher resistance than the gap metal lines, which is most likely also due to pitch walking.

Figure 11: Schematic of dual damascene metallization step, electrical resistance test structure and electrical resistance measurements through metal CD/Pitch for different metal trench populations corresponding to the 193i SAQP and EUV SADP process.

#### 3. OUTLOOK

Our first results for the EUV SADP dual damascene process show a better M2 wafer CDU and just slightly higher electrical resistance compared to our POR 193i SAQP process. This clearly demonstrates the ease of initiating an EUV SADP process compared to a 193i SAQP process. Additionally, we have shown a good CDU and overlay performance for our M2Block and Via 1 module. Next, the focus for improving the EUV SADP process lies in reducing line wiggling and pitch walking after low k etch as well as bringing the final CD closer to its target. Furthermore, the M2 EUV SADP module will be integrated with the M1 and M3 modules for further electrical testing. Additionally, the M2 EUV SADP module will also be used to study defectivity throughout the SADP patterning.

#### **REFERENCES**

- [1] Drapeau, M., Wiaux, V., Hendrickx, E., Verhaegen, S. & Machida, T. "Double patterning design split implementation and validation for the 32nm node." Proc. SPIE 6521, 83–97 (2007).

- [2] Suh, H. S., Mannaert, G., Vandenbroeck, N., Doise, J. & Doise, J. "Development of high-chi directed self-assembly process based on key learning from PS-b-PMMA system," Proc. SPIE 11612, (2021).

- [3] Bencher, C., Yongmei, C., Huixiong, D., Warren, M., Lior, H. "22nm half-pitch patterning by CVD spacer self alignment double patterning (SADP)" Proc. SPIE 6924, 1440–1446 (2008).

- [4] Altamirano-Sánchez, E., Tao, Z., Gunay-Demirkol, A., Lorusso, G., Hopf, T., Everaert, J.-L., Clark, W., Constantoudis, V., Sobieski, D., Ou, F. S., Hellin, D. "Self-aligned quadruple patterning to meet requirements for fins with high density," SPIE Newsroom (2016).

- [5] Briggs, B., Wilson, C. J., Devriendt, K., van der Veen, M. H., Decoster, S., Paolillo, S., Versluijs, J., Kesters, E., Sebaai, F., Jourdan, N., El-Mekki, Z., Heylen, N., Verdonck, P., Wan, D., Pedreira, O. V., Croes, K., Dutta, S., Ryckaert, J., Mallik, A., ... Tokei, Z. "N5 Technology Node Dual-Damascene Interconnects Enabled Using Multi Patterning," IITC (2017).

- [6] Decoster, S., Lazzarino, F., Vangoidsenhoven, D., Carballo, V. B., Tamaddon, A., Decoster, al S., B Carballo, V. M., Kesters, E., Lorant, C. "Exploration of EUV-based self-aligned multipatterning options targeting pitches below 20nm," Proc. SPIE 10960, 40–48 (2019).

- [7] Chen, H. P., Wu, Y. H., Huang, H. Y., Tsai, C. H., Lee, S. K., Lee, C. C., Wei, T. H., Yao, H. C., Wang, Y. C., Liao, C. Y., Chang, H. K., Lu, C. W., Shue, W. S., Cao, M. "Fully Self-Aligned Via Integration for Interconnect Scaling Beyond 3nm Node; Fully Self-Aligned Via Integration for Interconnect Scaling Beyond 3nm Node," IEDM (2021).

- [8] Montero, D., Vega-Gonzalez, V., Feurprier, Y., Varela Pedreira, O., Oikawa, N., Martinez, G. T., Batuk, D., Puliyalil, H., Versluijs, J., Decoster, H., Bazzazian, N., Jourdan, N., Kumar, K., Lazzarino, F., Murdoch, G., Park, S., Tokei, Z. "Enabling 3-level High Aspect Ratio Supervias for 3nm nodes and below; Enabling 3-level High Aspect Ratio Supervias for 3nm nodes and below," IITC (2022).

- [9] Chehab, B., Zografos, O., Litta, E. D., Ahmed, Z., Schuddinck, P., Jang, D., Hellings, G., Spessot, A., Weckx, P., Ryckaert, J. "Two-level MOL and VHV routing style to enable extreme height scaling beyond 2nm technology node," IITC (2021).

- [10] van der Veen, M., Heylen, N., Lariviere, S., Vega Gonzalez, V., Kesters, E., Le, Q. T., Teugels, L., Chew, S. A., Philipsen, H., Hung, J., Adelmann, C., Vanstreels, K., Jourdan, N., Holsteyns, F., Struyf, H., Wilson, C., Tokei, Z. "Co and Ru dual damascene compatible metallization studies," IITC (2019).

- [11] Murdoch, G., O'toole, M., Marti, G., Pokhrel, A., Tsvetanova, D., Decoster, S., Kundu, S., Oniki, Y., Thiam, A., Le, Q. T., Pedreira, O. V., Lesniewska, A., Martinez-Alanis, G., Park, S., Tokei, Z. "First demonstration of Two Metal Level Semi-damascene Interconnects with Fully Self-aligned Vias at 18MP," VLSI Technology and Circuits (2022).