Received 5 October 2023, accepted 22 October 2023, date of publication 1 November 2023, date of current version 17 November 2023. Digital Object Identifier 10.1109/ACCESS.2023.3329077

# **RESEARCH ARTICLE**

# **A Pragmatic Model to Predict Future Device Aging**

JAMES BROWN<sup>®1</sup>, KEAN HONG TOK<sup>1</sup>, RUI GAO<sup>®2</sup>, ZHIGANG JI<sup>®3</sup>, WEIDONG ZHANG<sup>®1</sup>, JOHN S. MARSLAND<sup>1</sup>, THOMAS CHIARELLA<sup>®4</sup>, JACOPO FRANCO<sup>®4</sup>, BEN KACZER<sup>®4</sup>, DIMITRI LINTEN<sup>4</sup>, (Senior Member, IEEE), AND JIAN FU ZHANG<sup>®1</sup>

<sup>1</sup>School of Engineering, Liverpool John Moores University, L3 3AF Liverpool, U.K.

<sup>2</sup>Electronics Research Institute of the Ministry of Industry and Information Technology, Guangzhou 511370, China <sup>3</sup>School of Microelectronics, Shanghai Jiaotong University, Shanghai 200240, China

<sup>4</sup>IMEC, 3001 Leuven, Belgium

Corresponding author: Jian Fu Zhang (j.f.zhang@ljmu.ac.uk)

This work was supported by the Engineering and Physical Science Research Council of U.K. under Grant EP/T026022/1.

**ABSTRACT** To predict long term device aging under use bias, models extracted from voltage accelerated tests must be extrapolated into the future. The traditional model uses a power law, to linearly fit the test data on a log-log plot, and then extrapolates aging kinetics. The challenge is that the measured data do not always follow a straight line on the log-log plot, calling the accuracy of such prediction into question. Although there are models that can fit test data well in this case, their prediction capability for future aging is typically not verified. The key advance of this work is the development of a methodology for extracting models that can verifiably predict future aging over a wide (Vg, Vd) bias space, when aging kinetics do not follow a simple power law. This is achieved by experimentally separating aging into four types of traps and modelling each of them by a straight line individually. The applicability of this methodology is verified on 3 different CMOS processes where it can predict aging at least 3 orders of magnitude into the future. The contributions of each type of traps across the (Vg, Vd) space are mapped. It is also shown that good fitting with test data does not warrant good prediction, so that good fitting should not be used as the only criterion for validating a model.

**INDEX TERMS** Hot carriers, BTI, aging, degradation, lifetime, instability, device-to-device variations, time dependent variations.

#### I. INTRODUCTION

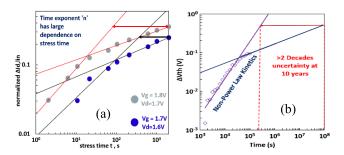

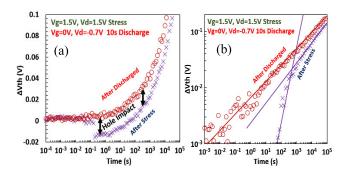

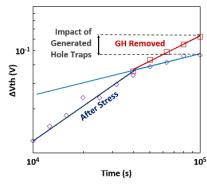

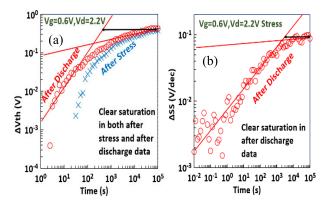

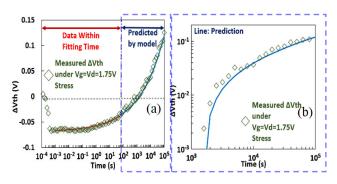

Predicting long term device aging under use bias has been a key challenge for CMOS technologies since their earliest usage. Despite early efforts [1], [2], [3], [4], [5], [6], [7], [8], [9], [10], [11], [12], [13], [14], [15], [16], [17], [18], [19], [20], [21], [22], [23], [24], [25], [26], [27], [28] accurately modelling and predicting future device aging remains an area of significant developmental effort for modern CMOS technologies. Hot Carrier aging (HCA), in particular, still offers many challenges and a reliable model for future aging prediction has yet to be verified across the (Vg, Vd) bias space. A major issue for predicting future degradation is that the kinetics of HCA do not always follow an ideal power law. Fig. 1(a) shows one example of this case reported by early work [3] and Fig. 1(b) gives one example recorded in this

The associate editor coordinating the review of this manuscript and approving it for publication was Jiajie Fan<sup>(D)</sup>.

work. Some recently proposed models can fit this non-power law behavior well. However, their ability to predict future aging has not been verified [3], [6], [10], [12], [14], [16], [25], [26], [27]. It will be shown that good fitting with test data does not warrant good prediction. Fig. 1 shows how the deviation from an ideal power law causes uncertainty in the predicted future device aging through extrapolation. There is a clear need for the development of an aging model that can not only fit test data, but also predict future aging across the (Vg, Vd) space.

The key advances of this work are: (i) Develop a measurement technique that separates the aging into four components; (ii) Develop a methodology for modelling aging by fitting the four components separately, rather than fitting the measured data directly; (iii) Experimentally verify the capability of the model extracted by our methodology to predict future aging.

The four separated components are as grown and generated electron and hole traps. It is shown that each type of trap can

**FIGURE 1.** Examples from early work [3] (a) and this work (b), showing how aging kinetics deviate from power law, making future aging prediction challenging.

be modelled by a straight line, enabling reliable extrapolation. The model extracted by this method can predict device aging at least 3 orders of magnitude ahead, thus bridging the gap between a feasible test duration of a few days and the 10-year operating lifetime required.

#### **II. DEVICES AND EXPERIMENTAL SETUP**

The methodology is first used to model aging for Fin-FETs comparable to a 22 nm node technology with channel width/length of 1/0.028  $\mu$ m. The applicability of the methodology is also verified on devices fabricated by a commercial 28 nm HKMG (Hi-k Metal Gate) process of 180/27 nm, and a 45 nm Gate-First HKMG process of 1/0.07  $\mu$ m, to show that it is generally applicable to different types of CMOS technologies.

If not otherwise specified, FinFETs were used and measurements were taken at 125 °C using fast pulse ( $10\mu$ s) Id ~ Vg (IV) supplied by WGFMU units, connected to a Keysight B1500A Semiconductor Analyzer. The threshold voltage, Vth, was extracted from each measured IV by using the maximum transconductance technique [20]. Idlin was extracted at Vg = 0.9 V, Vd = 0.1 V, and Idsat was extracted at Vg = Vd = 0.9 V.

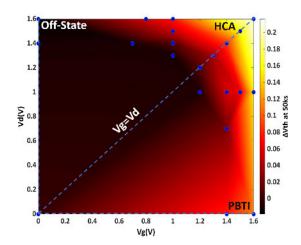

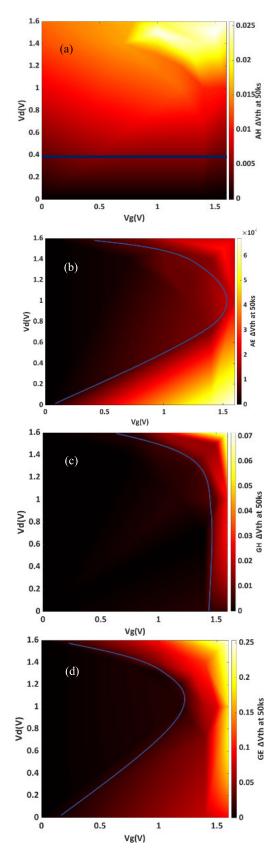

FIGURE 2.  $\Delta$  Vth over (Vg, Vd) space after 50ks stresses. Circles indicate sampled stress voltages.

# 127726

# III. A FRAMEWORK OF DEFECTS AND THE MODEL

### A. THE FRAMEWORK

It is well known that both electron and hole traps exist in the gate dielectric of MOSFETs [29], [30], [31], [32], [33]. In the gate dielectric, electron traps capture electrons and cause an increase in Vth, i.e. the shift  $\Delta$ Vth > 0. On the other hand, hole traps capture holes, causing a decrease in Vth, i.e.  $\Delta$ Vth < 0. For bias temperature instability (BTI), only one of them is commonly considered: electron traps for PBTI [34] and hole traps for NBTI [35]. For the full (Vg, Vd) space (Fig. 2), however, the gate can be either positive or negative relative to different regions of the substrate. For instance, under 0 < Vg < Vd, the relative gate voltage is positive near source, but negative near drain, resulting in different types of traps being active in different regions of the device.

For a model to be applicable to a wide range of (Vg, Vd) bias conditions, the defect framework should include both electron and hole traps in principle as both can contribute to aging under different conditions. Moreover, it has been reported that new electron and hole traps can be generated [29], [30], [34], [35]. This leads to four types of defects: As-grown electron traps (AE), Generated electron traps (GE), As-grown hole traps (AH), and Generated hole traps (GH). The challenge is how to separate them experimentally, model them individually, and then combine their impacts to give an accurate model of aging kinetics.

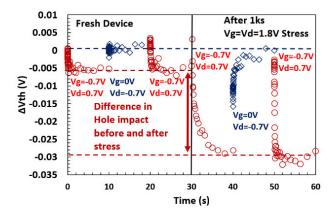

The left side of Fig. 3 shows the presence of AH in a fresh device, which can be charged and discharged repeatedly through alternating hole charging and discharging voltage conditions. When the hole charging voltages (Vg = -0.7 V, Vd = +0.7 V have been applied, the  $\Delta V$ th is negative relative to the reference level of fresh device (see the symbol 'o'), indicating the presence of trapped holes. When the discharge voltages (Vg = 0, Vd = -0.7 V) is applied, the symbol ' $\diamond$ ' shows that  $\Delta V$ th returns to zero, i.e. the fresh device level, indicating that the trapped holes have been discharged back to neutral level. Repeating the hole charging leads to reach the same level of trapped holes, as shown by the second set of symbol 'o' in the left side of Fig. 3. As the trapping level has not increased, it supports that new hole traps are not generated during the hole charging and discharging processes. In another word, the hole trapping observed in the left side of Fig. 3 comes from as-grown hole traps.

After stress (the stress step is not shown in Fig. 3), the same hole charging/discharging conditions were applied. The right side of Fig. 3 shows that the cyclable hole traps have clearly increased, when compared with that on the left side. This increase supports that new hole traps must be generated by the stress.

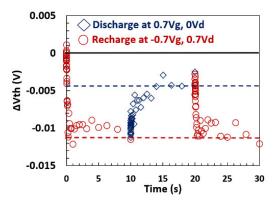

As will be described in Section III-B, to separate electron traps from hole traps, we need to find a bias condition for efficiently discharging hole traps. After scoping tests designed to find a condition that will fully discharge hole traps, without causing further aging, Vg = 0 and Vd = -0.7 V is chosen, where discharging completes in 10 sec, i.e. the symbol ' $\diamond$ '

**FIGURE 3.** Demonstration of how the as-grown hole traps in a fresh device can be charged-discharged repeatedly (left) and the increase of hole traps after stressing (right).

FIGURE 4. Charging and discharging of as grown hole traps under Vg = +0.7 V and Vd = 0 V.

returns to zero as shown in Fig. 3. To test whether drain or gate bias is more effective, discharging was also tested under Vg = +0.7 V, Vd = 0 and Fig. 4 shows that discharging does not complete back to the fresh level in 10 sec under this condition, indicating that negative bias applied to the drain is more effective at discharging the AH defects.

# B. DEFECT SEPARATION AND JUSTIFICATION FOR THE FRAMEWORK

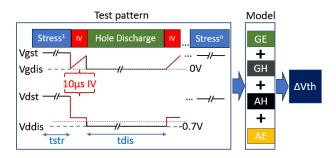

Test starts by measuring Id versus Vg (IV) on a fresh device, which is used to extract the reference Vth for evaluating aging induced shift. Fig. 5 shows a typical result obtained by following the proposed test pattern in Fig. 6. After stress reaches a preset time, it is interrupted and the first 'IV' marked in Fig. 6 is taken. The threshold voltage shift,  $\Delta$ Vth, extracted is given as the symbol '×' in Fig. 5(a). The  $\Delta$ Vth is negative at short time due to hole trapping, before electron trapping eventually turns it to positive during hot carrier aging (HCA). The negative  $\Delta$ Vth at short time cannot be plotted on a logarithmic scale. One can plot only the positive  $\Delta$ Vth at later time on the log-scale, but the symbol '×' in Fig. 5(b) shows that it does not follow a straight line, making extrapolation difficult. This motivates us to develop a technique to separate electron traps from hole traps.

Fig. 6 shows the new proposed methodology where a hole discharging step is inserted after measuring the first IV at each measurement point of the traditional measure-stress-measure procedure. Based on the results in Figs. 3 and 4, hole discharging was carried out under Vgdis = 0 V, Vddis = -0.7 V for tdis = 10 s. After this hole discharging step, the second IV in Fig. 6 is taken and the  $\Delta$ Vth evaluated from it is shown as the symbol 'o' in Figs. 5(a) and (b). As the trapped holes were neutralized, the symbol 'o' represents the  $\Delta$ Vth caused by electron trapping only.

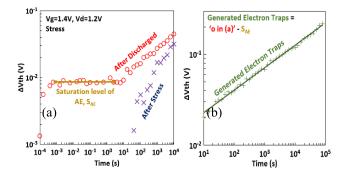

In many cases (typically stress conditions with Vg > Vd) after discharging trapped holes, the aging kinetics can have a flat region over several orders of magnitude in time before rising and an example is shown in Fig. 7(a). This flat region supports the presence of charged as-grown electron traps (AE). As filling as-grown traps reaches saturation quickly, their contribution to long term aging is taken from their saturation level,  $S_{AE}$ , in this work. By subtracting  $S_{AE}$  from the total electron trapping, the generated electron traps (GE) can be obtained, as shown in Fig. 7(b). The GE includes both electron traps in the gate dielectric and the generated acceptor-like interface traps. These two are not separated because the model with them combined can predict future aging well, as shown in section IV. As a pragmatic model, we would like to make it as simple as possible.

**FIGURE 5.** Measured  $\Delta V$ th immediately after-stress ('×') and after discharging trapped holes ('o') on a semi-log scale (a) and on a log-log scale (b).

FIGURE 6. Test pattern for separating trapped holes from trapped electrons. A hole-discharge step is inserted, and Id-Vg is recorded before and after this step.

**FIGURE 7.** (a) As grown electron traps are taken from the flat region of the data measured after discharging trapped holes. (b) Kinetics of the generated electron traps after subtracting the flat line in (a).

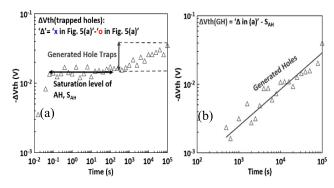

**FIGURE 8.** Contribution of trapped holes evaluated from the differences in  $\Delta V$ th measured pre- and post-discharging trapped holes (difference between 'x' and 'O' of Fig 5(a)). (b) The contribution of generated hole traps obtained by subtracting the flat line (AH) in (a).

To accurately model the measured  $\Delta$ Vth, i.e., the symbol '×' in Fig. 5(a), the contribution of hole traps to  $\Delta$ Vth must also be included. The hole trap contribution can be extracted from the difference between '×' and 'o' of Fig. 5(a). The hole trap contribution is plotted in Fig. 8(a). Fig. 8(a) shows that AH charging reaches a saturation level, S<sub>AH</sub>, rapidly, giving a flat region over two orders of magnitude in time. S<sub>AH</sub> can be used as the AH contribution for predicting future aging. Fig. 8(a) shows that, as stress time increases, | $\Delta$ Vth(Hole trap)| starts increasing without saturation, which is a signature of generating new hole traps (GH). To extract the kinetics of the GH, S<sub>AH</sub> is subtracted and Fig. 8(b) shows that GH can be fitted by a power law.

To show the impact of GH on the aging kinetics, Fig. 9 compares  $\Delta$ Vth before and after compensating GH by adding  $|\Delta$ Vth (GH)| to  $\Delta$ Vth (After Stress), as GH causes negative  $\Delta$ Vth. The results show that GH can make a substantial contribution to the reduction of aging slope.

Following this methodology, the aging model is given in the equation (1), which combines the four components: Generated electron traps (GE), Generated hole traps (GH), As-grown electron traps (AE), and As-grown hole traps (AH):

$$\Delta Vth = C_{GE}t^{n_{GE}} + C_{GH}t^{n_{GH}} + S_{AE} + S_{AH}, \qquad (1)$$

where C<sub>GE</sub> and C<sub>GH</sub> are voltage dependent constants.

**FIGURE 9.** When GH is compensated by ' $\Box$ ' = ' $\Diamond$ ' +| $\Delta$ Vth(GH)|, the 'soft saturation' is reduced.

#### **IV. PREDICTIVE MODELING**

#### A. FUTURE AGING PREDICTION

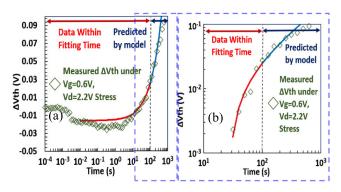

This section demonstrates that the extracted models can predict future aging. The data from short stress ( $\leq 100$  sec) is used to extract the parameters in equation (1). The model is then used to predict at least 3 orders of magnitude into the future. The accuracy of the prediction is verified by comparing the prediction with the measured data between  $\sim 100$  sec and  $\sim 100$  ksec. 100ks is used as the maximum value here because of the practical limitation for continuous use of shared test facilities in the laboratory.

For stresses under different Vg/Vd ratios, the time exponents are different. It is important to verify the applicability of the methodology to predict future aging across the (Vg, Vd) space. This is carried out by showing the predictions for the three corners of Fig. 2: HCA (Vg = Vd), PBTI (Vg > 0V, Vd = 0V), and off-state stress (OSS, Vg = 0V, Vd > 0V).

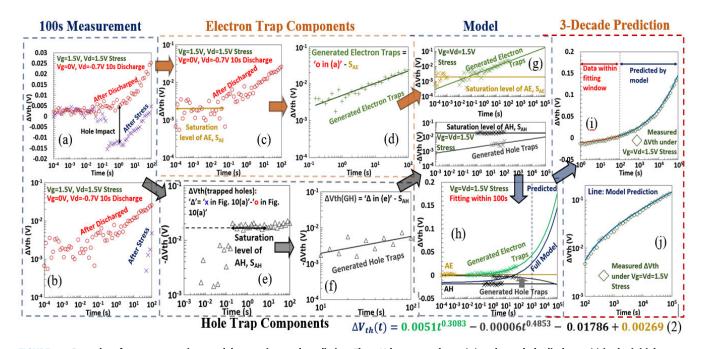

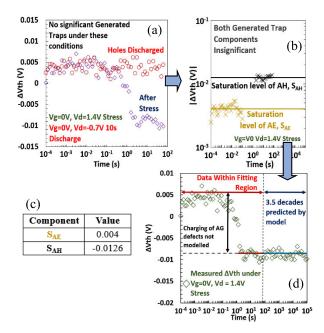

HCA under Vg = Vd: This is the most severe aging condition in the (Vg, Vd) stress space (Fig. 2). Fig. 10 shows the full process of extracting the model from 100s of measured data. Fig. 10(a)&(b) show the measured data in 100s pre- (symbol '×') and post-hole discharging (symbol 'o') in linear and logarithmic scale, respectively. The saturation level of as-grown electron traps,  $S_{AE}$ , is extracted from the flat region of  $\Delta$ Vth after hole-discharging, as shown by the line in Fig. 10(c). After subtracting  $S_{AE}$ , the contribution of generated electron traps (GE) is given in Fig. 10(d), which is fitted with a power law to extract  $C_{GE}$  and  $n_{GE}$  in equation (1).

Fig. 10(e) shows the contribution of hole traps, which was obtained from the difference between the pre- and post-hole discharge data in Fig. 10(a). Similar to AE, the flat region in Fig. 10(e) gives the saturation level of as-grown hole traps,  $S_{AH}$ . After subtracting  $S_{AH}$ , Fig. 10(f) gives the contribution of generated hole traps, which is then fitted with a power law to extract  $C_{GH}$  and  $n_{GH}$  in equation (1). The time range for extracting exponent is one decade or longer in this work. The  $\Delta$ Vth (GH) here is relatively small and a start time of 10 sec was chosen in Fig. 10(f) when  $\Delta$ Vth(GH) is  $\sim 2$  mV.

Fig. 10(g) shows the extracted four straight lines and they were extrapolated ahead by 3 orders of magnitude to  $10^5$  sec.

# **IEEE**Access

**FIGURE 10.** Procedure for trap separation, model extraction, and prediction. The  $\Delta V$ th measured pre- (×) and post-hole discharge (•) in the initial 100 s of stress under Vd = Vg = 1.5 V is used to create the model. (a) semi- log scale and (b) Log-Log scale. (c) The saturation level of as-grown electron trap is evaluated from the flat region (The line). (d) Generated electron traps are obtained by subtracting the flat line in (c). The line in (d) is fitted with power law. (e) Total contribution of trapped holes created by '×'-'o' in (a). The flat line is the saturation level of as-grown hole traps. (f) Generated hole traps are obtained by subtracting the flat line is the saturation level of as-grown hole traps. (f) Generated hole traps are obtained by subtracting the flat line in (c). The line in (c)-(f). (h) The 'Full model' is evaluated from equation (1) by combining the four lines in (g). (i) A comparison of the prediction by the 'Full model' (line) with test data (symbols) between 10<sup>2</sup> and 10<sup>5</sup> sec. The red line before 10<sup>2</sup> s is the fitted model. (j) A replot of the prediction region in Log-Log scale. RMSE of prediction = 3.05mV

Fig. 10(h) shows how the 4 lines in linear scale are combined through equation (1) to give the full  $\Delta V$ th. The predicted full  $\Delta V$ th between 100 and 10<sup>5</sup> sec is then compared with the measured data (symbols) in linear (Fig. 10(i)) and logscale (Fig. 10(j)), respectively. Good agreement has been achieved, even when the measured  $\Delta V$ th in Fig. 10(j) does not follow a simple power law. We believe that the success of this prediction originates from the transformation of the non-linear measured  $\Delta V$ th into four straight lines by our methodology and extrapolating straight lines is more reliable than extrapolating non-linear curves.

We do not have test data to verify that our model can predict aging beyond  $10^5$  sec. If we use all measured data up to  $10^5$  sec to extract the model, the GE in Fig. 10(d) and GH in Fig. 10(f) can be fitted over a larger time range, so that the two power laws in equation (1) can be fitted at least equally accurately. This leads to the expectation that the model extracted from data within  $10^5$  sec should also be able to predict at least 3 decades ahead, reaching ~10 years, if the aging is within the designed level for device lifetime definition, i.e.  $\Delta V$ th  $\leq 0.1V$  where aging saturation effects are insignificant.

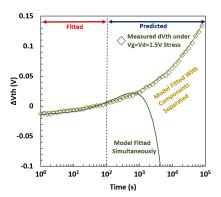

To demonstrate that separating into four components is essential for achieving the good prediction, we also fitted equation (1) directly with the test data in the fitting window of Fig. 10(i). Based on the least squared error, the parameters in equation (1) were simultaneously extracted. Fig. 11 shows

FIGURE 11. A comparison between accuracy of model in fitting and prediction regions when fitting was carried out by (1) separating into four components (as outlined in Fig.10) and (2) fitting all model parameters in equation (1) simultaneously with measured data based on least squares errors.

that good agreement was again obtained with the test data in the fitting window. When the fitted model was used to predict future aging, however, the agreement was poor.

To measure the agreement quantitatively, we use the Root-Mean-Square-Error (RMSE) between test data and the computed results by the model. Table 1 shows that, in the fitting region, direct simultaneous fitting can in fact give a slightly smaller RMSE than the separated fitting. In the prediction region, however, the simultaneously fitted parameters

TABLE 1. A comparison in RMSE between model when fitted by (1)

separating into four components and (2) fitting all model parameters in

equation (1) simultaneously with measured data based on least square

errors. The RMSE is in unit of Volt.

| Fitting Type     | RMSE (ΔVth)            |                                |

|------------------|------------------------|--------------------------------|

|                  | Fitting Region (<100s) | Prediction region (100s-100ks) |

| Separated Model  | 0.00196                | 0.00305                        |

| Simultaneous Fit | 0.00177                | 1.75719                        |

FIGURE 12. (a) Initial 63.1s of PBTI test data were used to create aging model. (b) Extraction and extrapolation of AE and GE components from initial data. Both AH and GH are insignificant under PBTI conditions. (c) Values for significant model parameters. (d) Comparison between the model prediction and test data. RMSE of prediction = 4.81mV.

clearly cannot be used to make prediction. These results demonstrate that good fitting does not warrant good prediction and should not be used as the criterion for validating a model. Instead, good prediction of future aging should be used to validate a model.

In sharp contrast with the poor prediction by the model when parameters were extracted through direct simultaneous fitting, Table 1 shows that the RMSE of the prediction three orders of magnitude ahead is only a few milli-volts, when the model parameters were extracted separately from the four components. This endorses our methodology for extracting the aging model.

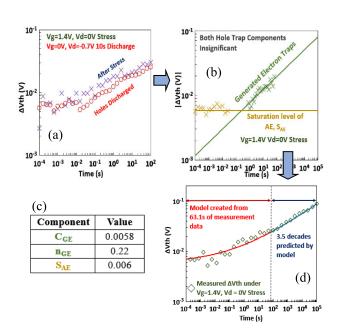

<u>PBTI (Vg > 0V, Vd = 0V)</u>: is another key condition of device aging. Fig. 12(a) shows how the initial 63 s of data are used to create the model. Under a PBTI stress the gate is positive over the whole channel as there is no drain voltage. This makes the hole trap contribution below the measurable level, so that AH and GH are set at 0 in the aging model. Figs. 12(b), 12(c) and 12(d) show the proposed methodology can be used to give good predictions, even when some components are insignificant.

**FIGURE 13.** (a) Initial 63.1 s of OSS test data were used to create the model. (b) The extraction and extrapolation of traps under OSS. (c) Values for significant model parameters. (d) Comparison between the model prediction and test data. RMSE of prediction = 0.87mV.

Off-state stress (OSS): Vg = 0V, Vd > 0V is the third corner of (Vg, Vd) stress space in Fig. 2. Under OSS, the electrical field within the device is strongly in favor of charging hole traps. Fig. 13 shows an example of modelling under an OSS condition. Fig. 13(a) shows the initial 63s of data used to extract the S<sub>AE</sub> and S<sub>AH</sub> shown Fig. 13(b). Their values are given in Fig. 13(c). In this case,  $\Delta$ Vth is dominated by AH, which saturates well within 10 seconds and changes little during the following 100 ksec, as shown in Fig. 13(d). Good prediction is verified in Fig. 13(d). At very high stress Vd, beyond the typical range of relevance for logic applications, OSS can generate hole traps. It is not shown here as it is outside the scope of this work.

# **B. PREDICTION OF AGING AT LOWER STRESS VOLTAGES**

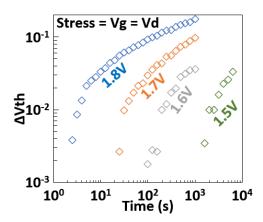

As device aging under use bias is typically too small to establish aging kinetics in a practical time, voltage-accelerated tests have been commonly used. To predict aging under use bias, it is essential to extrapolate the model extracted from stress voltage to the real use level, such as 0.9 V. Although the main thrust of this work is to propose a method for extracting the aging model that can predict future aging, we assess the accuracy of the voltage extrapolation under HCA with Vg = Vd here, since this is the most severe aging conditions in the (Vg, Vd) space of Fig. 2.

The stress voltages were varied between 1.5 V and 1.8 V and the extracted model will be used to predict the aging under 1.2 V. 1.2 V is selected because it is the lowest stress condition where aging kinetics can be reliably established within a reasonable time window (100 ksec).

**FIGURE 14.** The measured  $\Delta$ Vth pre-hole discharge under different stress biases on a commercial grade 28 nm process.

**FIGURE 15.** (a) The generated electron traps. The data from 1.5 - 1.8 V are fitted with power law to extract the n<sub>GE</sub> and C<sub>GE</sub> in equation (1). (b) The C<sub>GE</sub> extracted under different voltages can be fitted by the given equation.

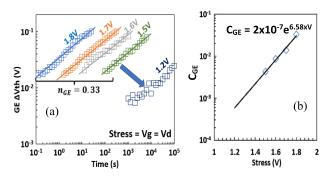

When the measured  $\Delta V$ th is plotted on the log-log scale, Fig. 14 shows that the aging kinetics under different stress voltages are not in parallel, making voltage prediction highly challenging. By following the methodology outlined in Section III, Fig. 15(a) shows that the separated GE under different voltages can be modelled well with a common time exponent of n<sub>GE</sub> = 0.33. The voltage dependent parameter, C<sub>GE</sub>, in equation (1) can be modelled by the formula given in Fig. 15(b).

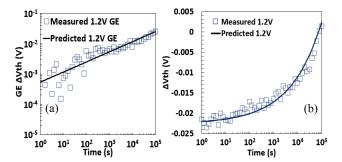

With  $n_{GE} = 0.33$  and  $C_{GE}$  at 1.2 V extrapolated using the formula in Fig. 15(b), the GE at 1.2 V can be predicted. Fig. 16(a) shows that the prediction (the line) agrees well with the test data with an RMSE of 1.46 mV.

The devices used here were made by a 28 nm commercial process as they have the smallest device-to-device variation. Under Vg = Vd, the measured GH is insignificant and was set to zero. The  $S_{AE}$  and  $S_{AH}$  in equation (1) under 1.2 V were measured. After combining the contributions from GE,  $S_{AE}$  and  $S_{AH}$ , Fig. 16(b) shows that the predicted  $\Delta$ Vth by equation (1) (the line) agrees well with the measured data. The model extracted from 1.5-1.8 V can be used to predict aging at 0.3 V below the lowest stress voltage used to create the model, therefore.

**FIGURE 16.** (a) A comparison of the GE predicted by the model extracted from the data between 1.5 and 1.8 V in Fig 15 with the measured one at 1.2 V. (b) The predicted  $\Delta$ Vth after-stress is compared to the measured value at 1.2 V after including the *AE* and *AH*. RMSE of predicted GE = 1.46mV

If we extract the model from the data obtained under 1.2-1.8 V, there will be more data points over a wide voltage range in Fig. 15(b) for extracting the parameters of  $C_{GE}$ . It is reasonable to assume that extracted model parameters will not be less accurate and can be used again to predict 0.3 V below the lowest stress voltage used to create the model, i.e. 1.2 V. This will reach the use bias of 0.9 V. Although we do not have the aging data at 0.9 V to verify it, we expect that the model has the potential to predict aging under use bias.

#### C. STRESS MAP OF THE FOUR TYPES OF DEFECTS

To develop a richer picture of how each type of defect responds to different stress conditions, 20 different conditions were applied to the FINFETs and the impact of each type of defect after 50 ksec was used to create the stress maps in Fig. 17. Blue lines on the stress maps are a rough guide to distinguish weak from strong impact regions.

Fig. 17(a) shows that as-grown hole traps (AH) have a heavy dependence on Vd. For a given high Vd, AH increases with Vg. As a result, the polarity of oxide field is not the only factor controlling AH and HC also plays a role in the charging of holes.

Fig. 17(b) shows that as-grown electron traps (AE) depend strongly on Vg and reach its maximum under PBTI. For a given high Vg, AE reduces initially with increasing Vd and then increases. The initial reduction is caused by lowering oxide field near drain, while the later rise can be caused by enhanced HC generation under high Vd.

Fig. 17(c) shows that the generated hole traps (GH) are strongest when both Vg and Vd are high and expand furthest into low Vg under Vg < Vd. Both HC and oxide field polarity play a role here. Finally, Fig. 17(d) shows the generated electron traps (GE) is strongest under Vg = Vd. GE reduces rapidly with lowering Vg, but the reduction is slower with lowering Vd. Both HC and oxide field contribute strongly to GE.

# D. SATURATION OF GENERATED INTERFACE STATES

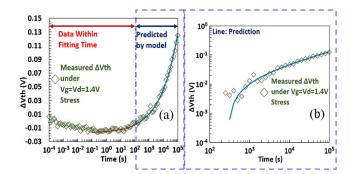

Under heavy stress conditions, Fig. 18(a) shows that there is soft saturation in aging kinetics, even after the hole traps

**FIGURE 17.** 2D stress map of the  $\Delta V$ th contribution from (a) the as-grown hole traps, (b) the as grown elestron traps, (c) the generated hole traps, (d) the generated electron traps at 50ks of stress.

**FIGURE 18.** (a) Example of aging kinetics where there is soft saturation in both the before and after hole discharge data. (b) Corresponding  $\triangle$ SS for  $\triangle$ Vth data shown in (a) also shows soft saturation.

**FIGURE 19.** Aging prediction within  $\triangle Vth < 0.1 V$  for a device with clear interface state induced saturation. (a) Semi- log scale (b) log-log scale. RMSE of prediction = 16.2mV.

were neutralized. This soft saturation cannot be explained by the generated hole traps, therefore. Early works [9], [14], [25], [26], [36], [37] have also reported soft saturation under such heavy stresses. One explanation for this behaviour is a saturation of generated interface states. As there is a limited number of interface state precursors [38], [39], the generated interface states will saturate when their precursors run out, leading to the saturation in Fig. 18(a). The change in the subthreshold swing ( $\Delta$ SS) was extracted, as generated interface states always increase  $\Delta$ SS. Fig. 18(b) shows how the  $\Delta$ SS also saturates, supporting the limitation in the generated interface states at high stress level.

As the saturation of generated interface states has not been considered in the proposed model, the model will not be able to predict this saturation. However, Fig. 18(a) shows that this saturation only occurs under heavy stress conditions and when the  $\Delta$ Vth is well beyond the level typically used to define lifetime of CMOS devices (<0.1 V). As the goal of the proposed model is to accurately model HCA within device lifetime, it is only important that  $\Delta$ Vth <0.1 V can still be predicted under such heavy stress conditions. Fig. 19 shows that this is the case.

**FIGURE 20.** Example of aging prediction in terms of  $\Delta$ Vth on a commercial grade 28 nm HKMG process in (a) semi-log scale (b) log-log scale. Test data are symbols and prediction is the line after 100 s. RMSE of prediction = 3.11mV.

**FIGURE 21.** Example of aging prediction in terms of  $\Delta V$ th on samples fabricated by a 45 nm process in (a) semi-log scale (b) log - log scale. Test data are symbols and prediction is the line after 100 s. RMSE of prediction = 5.97mV

# V. ALTERNATE PROCESSES, PROBES, AND **TEMPERATURES**

To fully demonstrate the applicability of the proposed methodology, this section gives examples of how the same technique can be used to make accurate aging predictions on different processes and probes. Firstly, examples of the predictive capability are shown on a commercial 28 nm HKMG process in Fig. 20. Secondly, Fig. 21 shows that the methodology is also applicable to the 45 nm process. The predictive capability of the methodology is generic, even though the extracted model parameters are process-specific.

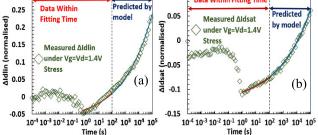

In addition to  $\Delta V$ th, the methodology is also applicable to other aging probes, i.e.  $\Delta$ Idlin/Idlin and  $\Delta$ Idsat/Idsat. Fig. 22(a) and 22(b) show the good predictive capability of the model in terms of  $\Delta$ Idlin/Idlin and  $\Delta$ Idsat/Idsat, respectively where the RMSE is within 1%.

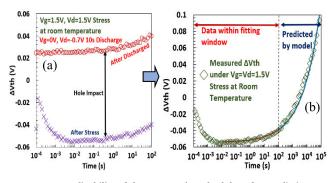

The tests up to here were carried out at 125 °C, but devices can operate at other temperatures. To demonstrate that the methodology is equally applicable at other temperatures, an example is given in Fig. 23, showing that prediction is also good at room temperature.

Finally, aging not only shifts threshold voltage and driving current, but also causes the stress induced leakage current (SILC) through the gate dielectric. It has been reported that the defects responsible for SILC act as 'step-stones' for **IEEE**Access

FIGURE 22. Example of aging prediction on the 22 nm FinFET process in terms of  $\Delta$ Idlin/Idlin (a) and  $\Delta$ Idsat/Idsat (b). RMSE of prediction is (a) 0.7% (b) 0.4%.

FIGURE 23. Applicability of the proposed methodology for predicting future ageing at room temperature. (a) The data within 100sec were used to extract the model parameter. (b) The extracted model (red line before 100 s ) predicts ageing 3 orders of magnitude ahead well. RMSE of prediction = 9.89mV

electrons passing through the dielectric and will not result in steady trapping [40]. Further work is needed to find if the methodology proposed here can be adapted to model the SILC.

### **VI. CONCLUSION**

0.3

A framework has been proposed for defects induced by aging over the (Vg,Vd) bias space. The four types of traps are as-grown electron traps, as-grown hole traps, generated electron traps, and generated hole traps. A measurement methodology has been developed to experimentally separate them. This methodology enables transforming the non-linear aging kinetics for the measured  $\Delta V$ th into linear ones for the four types of traps. As extrapolating straight lines is more reliable than extrapolating non-linear curves, we demonstrate that the straight lines extracted from short time (<100 sec) tests can be combined to predict future aging at least three orders of magnitude ahead. The methodology is applicable to different combinations of stress Vg and Vd, different aging probes, temperatures, and different CMOS technologies.

#### ACKNOWLEDGMENT

The authors thank IMEC and Qualcomm Technologies International Ltd. for supplying test samples.

### REFERENCES

- B. Marchand, G. Ghibaudo, F. Balestra, G. Guégan, and S. Deleonibus, "A new hot carrier degradation law for MOSFET lifetime prediction," *Microelectron. Rel.*, vol. 38, nos. 6–8, pp. 1103–1107, Jun. 1998, doi: 10.1016/S0026-2714(98)00137-1.

- [2] T. Nigam, B. Parameshwaran, and G. Krause, "Accurate product lifetime predictions based on device-level measurements," in *Proc. IEEE Int. Rel. Phys. Symp.*, Apr. 2009, pp. 634–639, doi: 10.1109/IRPS.2009. 5173322.

- [3] A. Makarov, B. Kaczer, P. Roussel, A. Chasin, M. Vandemaele, G. Hellings, A.-M. El-Sayed, M. Jech, T. Grasser, D. Linten, and S. Tyaginov, "Stochastic modeling of hot-carrier degradation in nFinFETs considering the impact of random traps and random dopants," in *Proc. 49th Eur. Solid-State Device Res. Conf. (ESSDERC)*, Sep. 2019, pp. 262–265, doi: 10.1109/ESSDERC.2019.8901721.

- [4] M. Duan, J. F. Zhang, A. Manut, Z. Ji, W. Zhang, A. Asenov, L. Gerrer, D. Reid, H. Razaidi, D. Vigar, V. Chandra, R. Aitken, B. Kaczer, and G. Groeseneken, "Hot carrier aging and its variation under use-bias: Kinetics, prediction, impact on vdd and SRAM," in *IEDM Tech. Dig.*, Dec. 2015, p. 20, doi: 10.1109/IEDM.2015.7409742.

- [5] M. Duan, J. F. Zhang, Z. Ji, W. D. Zhang, B. Kaczer, and A. Asenov, "Key issues and solutions for characterizing hot carrier aging of nanometer scale nMOSFETs," *IEEE Trans. Electron Devices*, vol. 64, no. 6, pp. 2478–2484, Jun. 2017, doi: 10.1109/TED.2017.2691008.

- [6] S. E. Tyaginov, E. Bury, A. Grill, Z. Yu, A. Makarov, A. De Keersgieter, M. I. Vexler, M. Vandemaele, R. Wang, A. Spessot, A. Chasin, and B. Kaczer, "On the contribution of secondary holes in hot-carrier degradation—A compact physics modeling perspective," in *Proc. 7th IEEE Electron Devices Technol. Manuf. Conf. (EDTM)*, Mar. 2023, pp. 3–5, doi: 10.1109/EDTM55494.2023.10103111.

- [7] M. Wang, P. Kulkarni, K. Cheng, A. Khakifirooz, V. S. Basker, H. Jagannathan, C. C. Yeh, V. Paruchuri, B. Doris, H. Bu, C. H. Lin, J. H. Stathis, K. Maitra, and P. J. Oldiges, "HOT-carrier degradation in undoped-body ETSOI FETS and SOI FINFETS," in *Proc. IEEE Int. Reliab. Phys. Symp.*, May 2010, pp. 1099–1104, doi: 10.1109/IRPS.2010.5488664.

- [8] R. Dreesen, K. Croes, J. Manca, W. De Ceuninck, L. De Schepper, A. Pergoot, and G. Groeseneken, "A new degradation model and lifetime extrapolation technique for lightly doped drain nMOSFETs under hotcarrier degradation," *Microelectron. Rel.*, vol. 41, no. 3, pp. 437–443, Mar. 2001, doi: 10.1016/S0026-2714(00)00225-0.

- [9] S. Mahapatra and U. Sharma, "A review of hot carrier degradation in n-channel MOSFETs—Part II: Technology scaling," *IEEE Trans. Electron Devices*, vol. 67, no. 7, pp. 2672–2681, Jul. 2020, doi: 10.1109/TED.2020.2994301.

- [10] S. Tyaginov, A. Grill, M. Vandemaele, T. Grasser, G. Hellings, A. Makarov, M. Jech, D. Linten, and B. Kaczer, "A compact physics analytical model for hot-carrier degradation," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2020, pp. 1–7, doi: 10.1109/IRPS45951.2020.9128327.

- [11] A. Chasin, J. Franco, R. Ritzenthaler, G. Hellings, M. Cho, Y. Sasaki, A. Subirats, P. Roussel, B. Kaczer, D. Linten, N. Horiguchi, G. Groeseneken, and A. Thean, "Hot-carrier analysis on nMOS Si FinFETs with solid source doped junction," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2016, pp. 1–6, doi: 10.1109/IRPS.2016.7574535.

- [12] M. Jech, S. Tyaginov, B. Kaczer, J. Franco, D. Jabs, C. Jungemann, M. Waltl, and T. Grasser, "First-principles parameter-free modeling of nand p-FET hot-carrier degradation," in *IEDM Tech. Dig.*, 2019, pp. 1–4.

- [13] J. Franco, B. Kaczer, A. Chasin, E. Bury, and D. Linten, "Hot electron and hot hole induced degradation of SiGe p-FinFETs studied by degradation maps in the entire bias space," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Mar. 2018, pp. 1–7, doi: 10.1109/IRPS.2018.8353601.

- [14] A. Makarov, S. E. Tyaginov, B. Kaczer, M. Jech, A. Chasin, A. Grill, G. Hellings, M. I. Vexler, D. Linten, and T. Grasser, "Hot-carrier degradation in FinFETs: Modeling, peculiarities, and impact of device topology," in *IEDM Tech. Dig.*, Dec. 2017, p. 13, doi: 10.1109/IEDM.2017.8268381.

- [15] L. Tielemans, R. Rongen, and W. De Ceuninck, "How reliable are reliability tests?" *Microelectron. Rel.*, vol. 42, nos. 9–11, pp. 1339–1345, Sep. 2002, doi: 10.1016/S0026-2714(02)00146-4.

- [16] M. Bina, S. Tyaginov, J. Franco, K. Rupp, Y. Wimmer, D. Osintsev, B. Kaczer, and T. Grasser, "Predictive hot-carrier modeling of n-channel MOSFETs," *IEEE Trans. Electron Devices*, vol. 61, no. 9, pp. 3103–3110, Sep. 2014, doi: 10.1109/TED.2014.2340575.

- [17] J. Kim, K. Hong, and H. Shin, "Analysis on temperature dependence of hot carrier degradation by mechanism separation," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 321–325, 2020, doi: 10.1109/JEDS.2020. 2981401.

- [18] R. Wang, Z. Sun, Y.-Y. Liu, Z. Yu, Z. Wang, X. Jiang, and R. Huang, "Understanding hot carrier reliability in FinFET technology from trap-based approach," in *IEDM Tech. Dig.*, Dec. 2021, p. 31, doi: 10.1109/IEDM19574.2021.9720674.

- [19] S. Mahapatra and R. Saikia, "On the universality of hot carrier degradation: Multiple probes, various operating regimes, and different MOSFET architectures," *IEEE Trans. Electron Devices*, vol. 65, no. 8, pp. 3088–3094, Aug. 2018, doi: 10.1109/TED.2018.2842129.

- [20] J. C. Liu, S. Mukhopadhyay, A. Kundu, S. H. Chen, H. C. Wang, D. S. Huang, J. H. Lee, M. I. Wang, R. Lu, S. S. Lin, Y. M. Chen, H. L. Shang, P. W. Wang, H. C. Lin, G. Yeap, and J. He, "A reliability enhanced 5nm CMOS technology featuring 5<sup>th</sup> generation FinFET with fully-developed EUV and high mobility channel for mobile SoC and high performance computing application," in *IEDM Tech. Dig.*, 2020, pp. 1–9, doi: 10.1109/IEDM13553.2020.9372009.

- [21] D. H. Huang, E. E. King, and L. J. Palkuti, "Improved method for evaluating hot-carrier aging in p-channel MOSFET's," in *Proc. 31st Annu. Proc. Rel. Phys.*, 1993, pp. 38–42.

- [22] J. H. Stathis, M. Wang, R. G. Southwick, E. Y. Wu, B. P. Linder, E. G. Liniger, G. Bonilla, and H. Kothari, "Reliability challenges for the 10 nm node and beyond," in *IEDM Tech. Dig.*, Dec. 2014, p. 20, doi: 10.1109/IEDM.2014.7047091.

- [23] P. Magnone, F. Crupi, N. Wils, R. Jain, H. Tuinhout, P. Andricciola, G. Giusi, and C. Fiegna, "Impact of hot carriers on nMOSFET variability in 45- and 65-nm CMOS technologies," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2347–2353, Aug. 2011, doi: 10.1109/TED.2011.2156414.

- [24] M. Bina, K. Rupp, S. Tyaginov, O. Triebl, and T. Grasser, "Modeling of hot carrier degradation using a spherical harmonics expansion of the bipolar Boltzmann transport equation," in *IEDM Tech. Dig.*, Dec. 2012, p. 30, doi: 10.1109/IEDM.2012.6479138.

- [25] S. Mahapatra, D. Saha, D. Varghese, and P. B. Kumar, "On the generation and recovery of interface traps in MOSFETs subjected to NBTI, FN, and HCI stress," *IEEE Trans. Electron Devices*, vol. 53, no. 7, pp. 1583–1592, Jul. 2006, doi: 10.1109/TED.2006.876041.

- [26] P. B. Vyas, N. Pimparkar, R. Tu, W. Arfaoui, G. Bossu, M. Siddabathula, S. Lehmann, J.-S. Goo, and A. B. Icel, "Reliability-conscious MOSFET compact modeling with focus on the defect-screening effect of hot-carrier injection," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Mar. 2021, pp. 1–4, doi: 10.1109/IRPS46558.2021.9405197.

- [27] S. Tyaginov, M. Bina, J. Franco, D. Osintsev, O. Triebl, B. Kaczer, and T. Grasser, "Physical modeling of hot-carrier degradation for short- and long-channel MOSFETs," in *Proc. IEEE Int. Reliab. Phys. Symp.*, 2014, pp. 1–8, doi: 10.1109/IRPS.2014.6861193.

- [28] M. Tsuno, M. Suga, M. Tanaka, K. Shibahara, M. Miura-Mattausch, and M. Hirose, "Physically-based threshold voltage determination for MOS-FET's of all gate lengths," *IEEE Trans. Electron Devices*, vol. 46, no. 7, pp. 1429–1434, Jul. 1999, doi: 10.1109/16.772487.

- [29] S. Tyaginov, I. Starkov, O. Triebl, H. Ceric, T. Grasser, H. Enichlmair, J. M. Park, and C. Jungemann, "Secondary generated holes as a crucial component for modeling of HC degradation in high-voltage n-MOSFET," in *Proc. Int. Conf. Simul. Semicond. Processes Devices*, 2011, pp. 123–126, doi: 10.1109/SISPAD.2011.6035065.

- [30] M. Jech, T. Grasser, and M. Waltl, "The importance of secondary generated carriers in modeling of full bias space," in *Proc. 6th IEEE Electron Devices Technol. Manuf. Conf.*, vol. 2, 2022, pp. 265–267, doi: 10.1109/edtm53872.2022.9798262.

- [31] M. Jech, G. Rott, H. Reisinger, S. Tyaginov, G. Rzepa, A. Grill, D. Jabs, C. Jungemann, M. Waltl, and T. Grasser, "Mixed hotcarrier/bias temperature instability degradation regimes in full V<sub>G</sub>, V<sub>D</sub> bias space: Implications and peculiarities," *IEEE Trans. Electron Devices*, vol. 67, no. 8, pp. 3315–3322, Aug. 2020, doi: 10.1109/TED.2020. 3000749.

- [32] P. Heremans, R. Bellens, G. Groeseneken, and H. E. Maes, "Comments on 'The generation and characterization of electron and hole traps created by hole injection during low gate voltage hot-carrier stressing of n-MOS transistors' [with reply]," *IEEE Trans. Electron Devices*, vol. 39, no. 2, pp. 458–464, Feb. 1992, doi: 10.1109/16.121710.

- [33] K. R. Hofmann, C. Werner, W. Weber, and G. Dorda, "Hot-electron and hole-emission effects in short n-channel MOSFET's," *IEEE Trans. Electron Devices*, vol. 32, no. 3, pp. 691–699, Mar. ED-1985.

- [34] R. Gao, Z. Ji, S. M. Hatta, J. F. Zhang, J. Franco, B. Kaczer, W. Zhang, M. Duan, S. De Gendt, D. Linten, G. Groeseneken, J. Bi, and M. Liu, "Predictive as-grown-generation (A-G) model for BTI-induced device/circuit level variations in nanoscale technology nodes," in *IEDM Tech. Dig.*, 2017, p. 31, doi: 10.1109/IEDM.2016.7838520.

- [35] R. Gao, Z. Ji, A. B. Manut, J. F. Zhang, J. Franco, S. W. M. Hatta, W. D. Zhang, B. Kaczer, D. Linten, and G. Groeseneken, "NBTIgenerated defects in nanoscaled devices: Fast characterization methodology and modeling," *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 4011–4017, Oct. 2017, doi: 10.1109/TED.2017.2742700.

- [36] D. Varghese, M. A. Alam, and B. Weir, "A generalized, I<sub>B</sub>-independent, physical HCI lifetime projection methodology based on universality of hot-carrier degradation," in *Proc. IEEE Int. Rel. Phys. Symp.*, May 2010, pp. 1091–1094, doi: 10.1109/IRPS.2010.5488666.

- [37] Y. Ding, C. Yan, Y. Qu, and Y. Zhao, "Re-examination of hot carrier degradation mechanism in ultra-scaled nFinFETs," *IEEE Electron Device Lett.*, vol. 43, no. 11, pp. 1802–1805, Nov. 2022, doi: 10.1109/LED.2022.3204429.

- [38] Z. Wu, J. Franco, B. Truijen, P. Roussel, B. Kaczer, D. Linten, and G. Groeseneken, "Investigation of the impact of hot-carrier-induced interface state generation on carrier mobility in nMOSFET," *IEEE Trans. Electron Devices*, vol. 68, no. 7, pp. 3246–3253, Jul. 2021, doi: 10.1109/TED.2021.3080657.

- [39] A. Stesmans, "Dissociation kinetics of hydrogen-passivated P<sub>b</sub> defects at the (111)Si/SiO<sub>2</sub> interface," *Phys. Rev. B, Condens. Matter*, vol. 61, no. 12, p. 8393, 2000.

- [40] C. Z. Zhao, M. B. Zahid, J. F. Zhang, G. Groeseneken, R. Degraeve, and S. De Gendt, "Properties and dynamic behavior of electron traps in HfO<sub>2</sub>/SiO<sub>2</sub> stacks," *Microelectronic Eng.*, vol. 80, pp. 366–369, Jun. 2005, doi: 10.1016/j.mee.2005.04.028.

**RUI GAO** received the bachelor's degree in microelectronics from Sun Yat-sen University, China, in 2011, the master's degree in microelectronics from Xidian University, China, in 2014, and the Ph.D. degree in microelectronics from Liverpool John Moores University, U.K., in 2018. Since 2018, he has been with the China Electronic Product Reliability and Environmental Testing Research Institute (CEPREI), Guangzhou, China. His research interests include the reliability char-

acterization of MOSFETs, GaN MIS-HEMTs, and RRAM.

**ZHIGANG JI** received the B.Eng. degree in electrical engineering from Tsinghua University, in 2003, the M.Eng. degree in microelectronics from Peking University, in 2006, and the Ph.D. degree in microelectronics from Liverpool John Moores University, in 2010. In 2020, he joined Shanghai Jiaotong University, where he is currently a Professor in nanoelectronics and the Director of the LEMON Laboratory. He has authored or coauthored over 200 scientific papers,

including IEDM and VLSI. His current research interests include nanoscale CMOS and non-CMOS devices, DTCO, and emerging technologies for applications, such as hardware security and new-paradigm computing.

JAMES BROWN was born in Liverpool, U.K., in 1994. He received the M.Eng. degree in electronics and electrical engineering and the Ph.D. degree in electronics and cyber security from Liverpool John Moores University, Liverpool, in 2017 and 2021, respectively.

Since 2021, he has been a Postdoctoral Research Fellow with Liverpool John Moores University. His primary research interests include low power cybersecurity primitives, such as true/quantum

random number generators and physically unclonanble functions, the characterization and reliability of nanoscale semiconductor devices, particularly hot carrier aging and random telegraph noise.

WEIDONG ZHANG received the Ph.D. degree from Liverpool John Moores University (LJMU), Liverpool, U.K., in 2003. He has been a Professor in nanoelectronics with LJMU, since 2014. His current research interests include the characterization and quality assessment of resistive switching and flash memory devices, ovonic threshold switching devices, CMOS devices based on Si, Ge, and 2D materials, GaN HEMT, and GaO devices.

**KEAN HONG TOK** received the B.Eng. degree in electrical and electronic engineering from Liverpool John Moores University (LJMU), Liverpool, U.K., in 2019, where he is currently pursuing the Ph.D. degree.

JOHN S. MARSLAND received the B.Sc. degree in electronics from the University of Southampton, Southampton, U.K., in 1983, and the Ph.D. degree from The University of Sheffield, Sheffield, U.K., in 1988. He was with the University of Liverpool, Liverpool, U.K., until 2017. Since 2017, he has been with the School of Engineering, Liverpool John Moores University, Liverpool. His current research interests include neural network implementation in hardware, including memristors and

low-level light detection using avalanche photodiodes.

Dr. Kaczer has served twice as the Chair of the Characterization, Reliabil-

ity and Yield Subcommittee of the International Electron Device Meeting (IEDM; 2007 and 2015) and a member of various subcommittees of the

IRPS (2002-2016). Since 2018, he has been serving as a member of IRPS

Management Committee. He was the General Chair of the Semiconductor

Interfaces Specialists Conference (SISC; 2006) and continues to act as the

Conference Secretary, since 2007. He co-organized the INFOS Conference, in 2005. He served on the INFOS, WoDiM, IPFA, and ICICDT conference

committees. He has served on the Editorial Board of IEEE JOURNAL OF

TRANSACTION OF ELECTRON DEVICES for three terms (2011-2019).

**THOMAS CHIARELLA** received the M.Sc. degree in electronics from Institut Supérieur Industriel Catholique du Hainaut, Charleroi, Belgium, in 2002. He directly joined the Silicon Process and Device Technology Division, IMEC, as a Characterization Engineer and took part, as s device engineer in technology transfers (130nm, 90nm, 65nm, 14nm) and the baseline yield improvement. He takes part in IMEC'S Affiliation Program focusing on successful and efficient definition and

evaluation of finFET, nanosheet, and CFET technologies. He is currently a Senior Researcher in charge of finFET and CFET device design. He has actively contributed to the Horizon 2020 ASCENT EU Project (Project no. 654384). In addition to own publications in ICMTS/ESSDERC proceedings and *Solid-State Electronics* journal, he contributed to more than 50 technical papers (mainly IEDM/VLSI).

**JACOPO FRANCO** received the B.Sc. and M.Sc. degrees in electrical engineering from the University of Calabria, Italy, in 2005 and 2008, respectively, and the Ph.D. degree in electrical engineering from KU Leuven, Belgium, in 2013. He is currently a Principal Member of Technical Staff with the Reliability Group, IMEC, Belgium. His research interests include CMOS FEOL reliability characterization, optimization, and modeling. He has (co)authored more than

250 contributed or invited papers and three patents. He was a recipient of seven IEEE awards. He has been serving in various functions on the committees of IRPS, SISC, IIRW, ESREF, WoDiM, and INFOS conferences. He was an Associate Editor of IEEE TRANSACTIONS ON DEVICE AND MATERIALS RELIABILITY and IEEE TRANSACTIONS ON ELECTRON DEVICES.

**DIMITRI LINTEN** (Senior Member, IEEE) received the Ph.D. degree in electrical engineering from Vrije Universiteit Brussels, Belgium, in 2006. He is currently the Head of the Advanced Reliability Robustness and Test Department (AR2T), IMEC. His current research interests include reliability, ESD, DFT and electrical testing, thermal and mechanical properties of IC's, hardware security, and radiation hardness.

**BEN KACZER** received the M.S. degree in physical electronics from Charles University, Prague, in 1992, and the M.S. and Ph.D. degrees in physics from The Ohio State University, in 1996 and 1998, respectively.

He is currently a Scientific Director with the FEOL Reliability Group (DRE), IMEC, Leuven, Belgium. For his Ph.D. research on the ballistic-electron emission microscopy of  $SiO_2$  and SiC films he received the OSU Presidential

Fellowship and support from Texas Instruments Inc. In 1998, he joined the Reliability Group, IMEC, where his activities have included the research of the degradation phenomena and reliability assessment of SiO<sub>2</sub>, SiON, high-k, and ferroelectric films, planar and multiple-gate FETs, circuits, and the characterization of Ge, SiGe, III-V, and MIM devices. He has coauthored more than 600 journals and conference papers and four patent groups related to device and circuit reliability, presented a number of invited papers and tutorials, and received six IEEE International Reliability Physics Symposium (IRPS) Best and Outstanding Paper Awards, two IEEE IPFA Best Paper Awards, and the 2011 IEEE EDS Paul Rappaport Award.

**JIAN FU ZHANG** received the B.Eng. degree in electrical engineering from Xi'an Jiao Tong University, in 1982, and the Ph.D. degree from the University of Liverpool, in 1987.

From 1986 to 1992, he was a Research Associate with the University of Liverpool. He joined Liverpool John Moores University (LJMU) as a Senior Lecturer, in 1992, became a Reader, in 1996, and a Professor, in 2001. He is currently the Area Leader for Microelectronics and

the Head of the Research Centre of Electrical and Electronic Engineering, LJMU. He is the author or coauthor of over 200 journals/conference papers, including 45 invited papers/book chapters/conference tutorials, 68 papers in IEEE TRANSACTIONS AND ELECTRON DEVICE LETTERS, and 20 papers at IEDM/Symposium of VLSI Technology. He is/was a member of the technical program committee of several international conferences, including IEDM. His current research interests include new materials and devices for future microelectronic industry; the qualification, modeling, and prediction of aging and RTN; new characterization techniques; hardware cybersecurity; and cool CMOS.

. . .